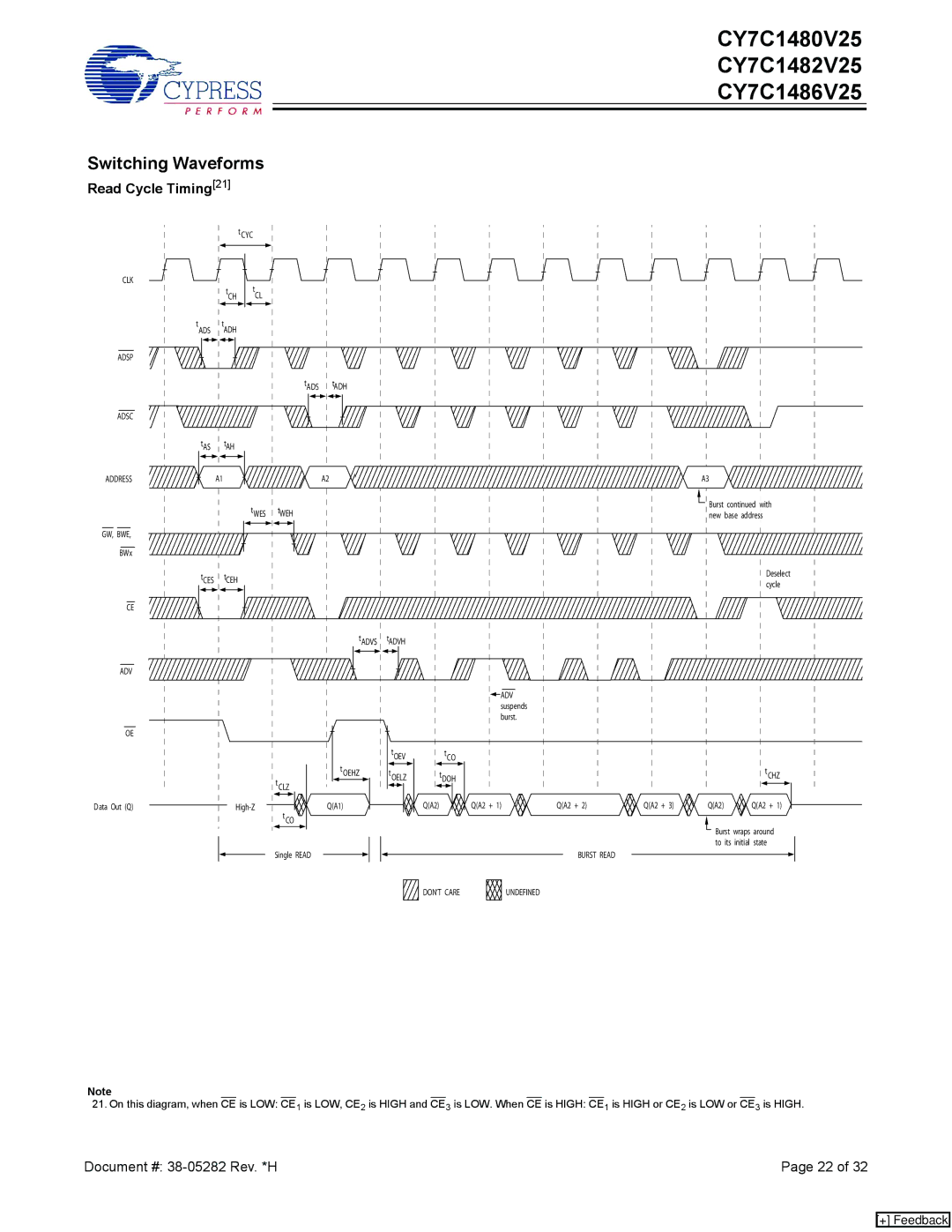

CLK

tCH

tADS tADH

ADSP

ADSC

tAS tAH

tCL

tADS tADH

ADDRESS

GW, BWE, BWx

A1

A2 | A3 |

tWES tWEH | Burst continued with |

new base address |

CE

ADV

OE

Data Out (Q)

tCES tCEH

| tADVS | tADVH |

|

|

|

|

|

|

|

| ADV |

|

|

|

|

|

| suspends |

|

|

|

|

|

| burst. |

|

|

|

| tOEV | tCO |

|

|

|

| tOEHZ | tOELZ | tDOH |

|

|

|

| tCLZ |

|

|

|

|

|

Q(A1) |

| Q(A2) | Q(A2 + 1) | Q(A2 + 2) | Q(A2 + 3) | |

| tCO |

|

|

|

|

|

| Single READ |

|

|

| BURST READ |

|

|

|

| DON’T CARE | UNDEFINED |

|

|

Deselect cycle

tCHZ

Q(A2) | Q(A2 + 1) |

Burst wraps around to its initial state

Note

21. On this diagram, when CE is LOW: CE1 is LOW, CE2 is HIGH and CE3 is LOW. When CE is HIGH: CE1 is HIGH or CE2 is LOW or CE3 is HIGH.

Document #: | Page 22 of 32 |

[+] Feedback