CY7C1480V25

CY7C1482V25

CY7C1486V25

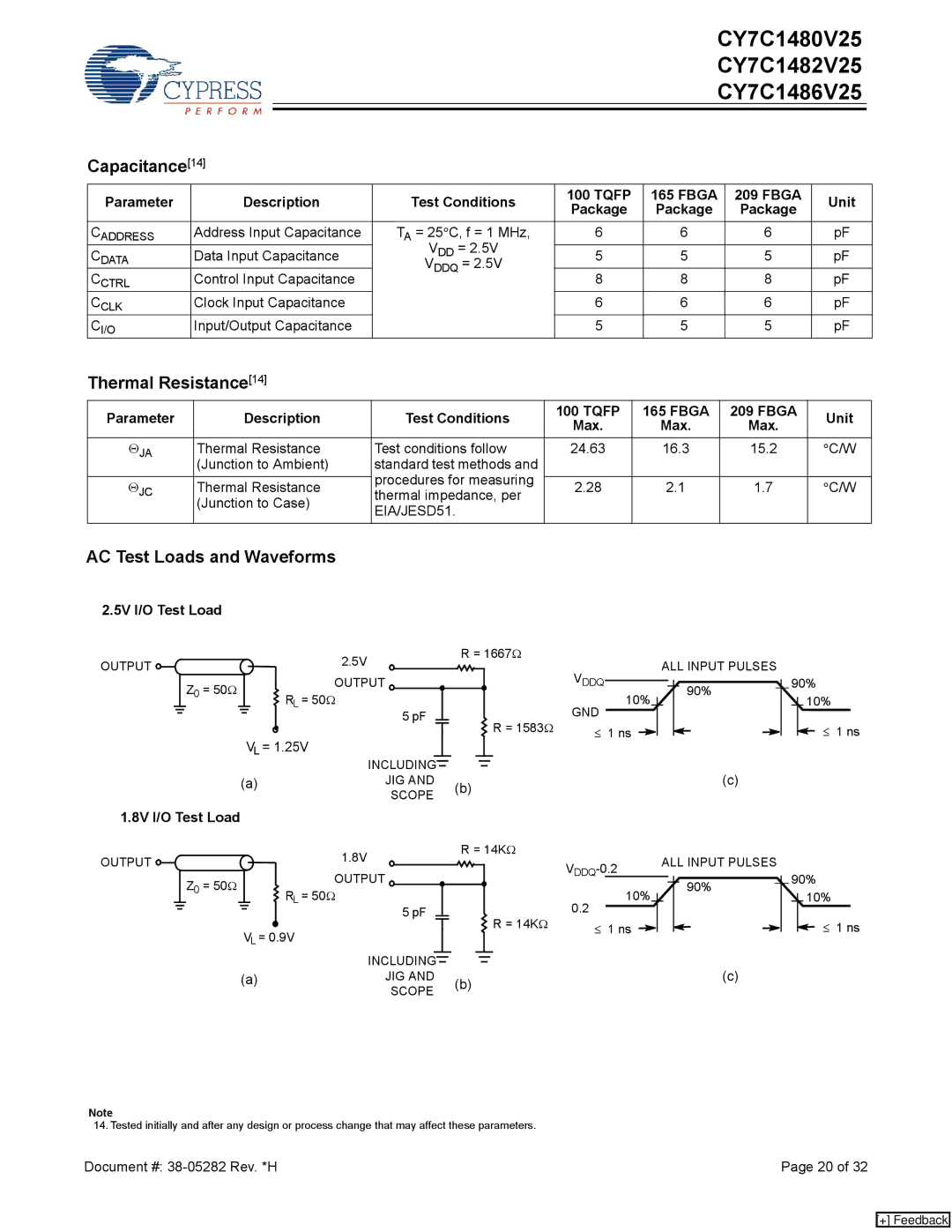

Capacitance[14]

Parameter | Description | Test Conditions | 100 TQFP | 165 FBGA | 209 FBGA | Unit | |

Package | Package | Package | |||||

|

|

|

| ||||

|

|

|

|

|

|

| |

CADDRESS | Address Input Capacitance | TA = 25°C, f = 1 MHz, | 6 | 6 | 6 | pF | |

|

| VDD = 2.5V |

|

|

|

| |

CDATA | Data Input Capacitance | 5 | 5 | 5 | pF | ||

VDDQ = 2.5V | |||||||

CCTRL | Control Input Capacitance | 8 | 8 | 8 | pF | ||

| |||||||

CCLK | Clock Input Capacitance |

| 6 | 6 | 6 | pF | |

CI/O | Input/Output Capacitance |

| 5 | 5 | 5 | pF |

Thermal Resistance[14]

Parameter | Description | Test Conditions | 100 TQFP | 165 FBGA | 209 FBGA | Unit | |

Max. | Max. | Max. | |||||

|

|

|

| ||||

|

|

|

|

|

|

| |

ΘJA | Thermal Resistance | Test conditions follow | 24.63 | 16.3 | 15.2 | °C/W | |

| (Junction to Ambient) | standard test methods and |

|

|

|

| |

|

| procedures for measuring |

|

|

|

| |

ΘJC | Thermal Resistance | 2.28 | 2.1 | 1.7 | °C/W | ||

thermal impedance, per | |||||||

| (Junction to Case) | EIA/JESD51. |

|

|

|

| |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

AC Test Loads and Waveforms

2.5V I/O Test Load

OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

| 2.5V |

|

|

| R = 1667Ω |

|

|

|

|

| ALL INPUT PULSES | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VDDQ |

|

|

|

| ||||||||||||||

|

|

|

|

|

|

| Z0 | = 50Ω |

|

|

| OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

| RL = 50Ω |

|

|

|

|

|

|

|

|

|

|

|

|

| 10% |

|

|

|

| 90% |

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 pF |

|

|

|

|

|

|

|

|

|

|

|

|

| R = 1583Ω | GND |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ≤ 1 ns |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| VL = 1.25V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| INCLUDING |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (c) | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| (a) | JIG AND |

| (b) |

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| SCOPE |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

1.8V I/O Test Load |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

| 1.8V |

|

|

| R = 14KΩ |

|

|

|

|

| ALL INPUT PULSES | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

|

| Z0 | = 50Ω |

|

|

| OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

| RL = 50Ω |

|

|

|

|

|

|

|

|

|

|

|

|

| 10% |

|

| 90% |

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 pF |

|

|

|

|

|

|

|

|

|

|

|

|

| R = 14KΩ | 0.2 |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ≤ 1 ns |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| VL = 0.9V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| INCLUDING |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (c) | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| (a) | JIG AND |

| (b) |

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| SCOPE |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

90%

10%

≤ 1 ns

90%

10%

≤ 1 ns

Note

14. Tested initially and after any design or process change that may affect these parameters.

Document #: | Page 20 of 32 |

[+] Feedback