CY7C1480V25

CY7C1482V25

CY7C1486V25

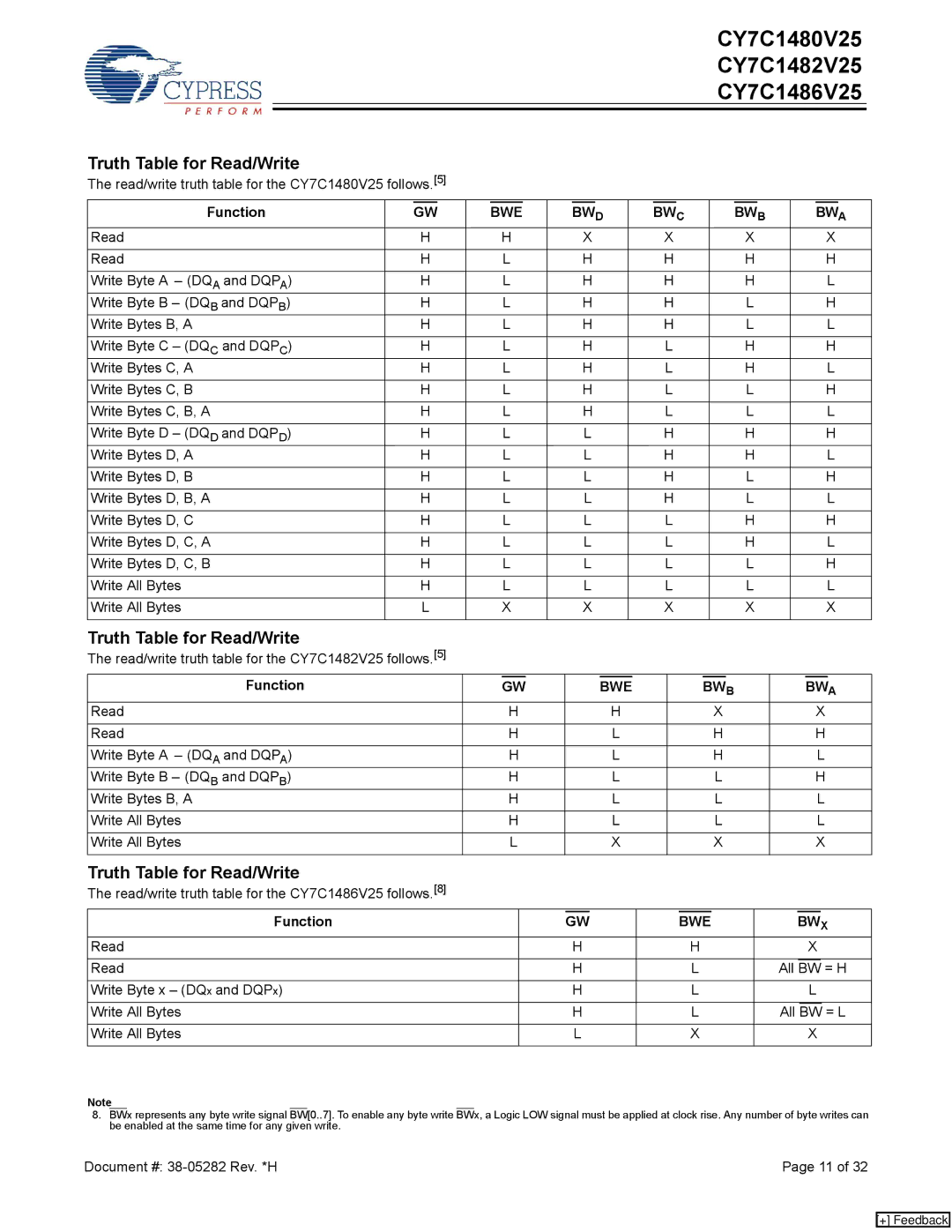

Truth Table for Read/Write

The read/write truth table for the CY7C1480V25 follows.[5]

Function | GW | BWE | BWD | BWC | BWB | BWA |

Read | H | H | X | X | X | X |

|

|

|

|

|

|

|

Read | H | L | H | H | H | H |

|

|

|

|

|

|

|

Write Byte A – (DQA and DQPA) | H | L | H | H | H | L |

Write Byte B – (DQB and DQPB) | H | L | H | H | L | H |

Write Bytes B, A | H | L | H | H | L | L |

|

|

|

|

|

|

|

Write Byte C – (DQC and DQPC) | H | L | H | L | H | H |

Write Bytes C, A | H | L | H | L | H | L |

|

|

|

|

|

|

|

Write Bytes C, B | H | L | H | L | L | H |

|

|

|

|

|

|

|

Write Bytes C, B, A | H | L | H | L | L | L |

|

|

|

|

|

|

|

Write Byte D – (DQD and DQPD) | H | L | L | H | H | H |

Write Bytes D, A | H | L | L | H | H | L |

|

|

|

|

|

|

|

Write Bytes D, B | H | L | L | H | L | H |

|

|

|

|

|

|

|

Write Bytes D, B, A | H | L | L | H | L | L |

|

|

|

|

|

|

|

Write Bytes D, C | H | L | L | L | H | H |

|

|

|

|

|

|

|

Write Bytes D, C, A | H | L | L | L | H | L |

|

|

|

|

|

|

|

Write Bytes D, C, B | H | L | L | L | L | H |

|

|

|

|

|

|

|

Write All Bytes | H | L | L | L | L | L |

|

|

|

|

|

|

|

Write All Bytes | L | X | X | X | X | X |

|

|

|

|

|

|

|

Truth Table for Read/Write

The read/write truth table for the CY7C1482V25 follows.[5]

Function |

| GW |

|

| BWE |

|

| BW | B |

| BW | A |

|

|

|

|

|

|

|

|

|

|

| ||

Read |

| H |

|

| H |

|

| X |

| X | ||

|

|

|

|

|

|

|

|

|

|

| ||

Read |

| H |

|

| L |

|

| H |

| H | ||

|

|

|

|

|

|

|

|

|

|

| ||

Write Byte A – (DQA and DQPA) |

| H |

|

| L |

|

| H |

| L | ||

Write Byte B – (DQB and DQPB) |

| H |

|

| L |

|

| L |

| H | ||

Write Bytes B, A |

| H |

|

| L |

|

| L |

| L | ||

|

|

|

|

|

|

|

|

|

|

| ||

Write All Bytes |

| H |

|

| L |

|

| L |

| L | ||

|

|

|

|

|

|

|

|

|

|

| ||

Write All Bytes |

| L |

|

| X |

|

| X |

| X | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

Truth Table for Read/Write

The read/write truth table for the CY7C1486V25 follows.[8]

Function | GW |

|

| BWE | BWX | ||||

Read | H |

|

| H |

|

| X | ||

|

|

|

|

|

|

|

|

|

|

Read | H |

|

| L | All | BW |

| = H | |

Write Byte x – (DQx and DQPx) | H |

|

| L |

|

| L | ||

|

|

|

|

|

|

|

| ||

Write All Bytes | H |

|

| L | All | BW | = L | ||

|

|

|

|

|

|

|

| ||

Write All Bytes | L |

|

| X |

|

| X | ||

|

|

|

|

|

|

|

|

|

|

Note

8.BWx represents any byte write signal BW[0..7]. To enable any byte write BWx, a Logic LOW signal must be applied at clock rise. Any number of byte writes can be enabled at the same time for any given write.

Document #: | Page 11 of 32 |

[+] Feedback