CY7C6431x

CY7C64345, CY7C6435x

enCoRe™ V Full Speed USB Controller

Features

■Powerful Harvard Architecture Processor

❐M8C processor speeds running up to 24 MHz

❐Low power at high processing speeds

❐Interrupt controller

❐3.0V to 5.5V operating voltage without USB

❐Operating voltage with USB enabled:

•3.15 to 3.45V when supply voltage is around 3.3V

•4.35 to 5.25V when supply voltage is around 5.0V

❐Temperature range: 0°C to 70°C

■Flexible

❐Up to 32K Flash program storage

•50,000 erase and write cycles

•Flexible protection modes

❐Up to 2048 bytes SRAM data storage

❐

■Complete Development Tools

❐Free development tool (PSoC Designer™)

❐Full featured,

❐Full speed emulation

❐Complex breakpoint structure

❐128K trace memory

■Precision, Programmable Clocking

❐

❐Internal ±5.0% 6, 12, or 24 MHz main oscillator

•0.25% accuracy with Oscillator Lock to USB data, no external components required

•Internal low speed oscillator at 32 kHz for watchdog and sleep. The frequency range is 19 to 50 kHz with a 32 kHz typical value

■Programmable Pin Configurations

❐25 mA sink current on all GPIO

❐Pull Up, High Z, Open Drain, CMOS drive modes on all GPIO

❐Configurable inputs on all GPIO

❐Low dropout voltage regulator for Port 1 pins. Programmable to output 3.0, 2.5, or 1.8V at the I/O pins

❐Selectable, regulated digital I/O on Port 1

•Configurable input threshold for Port 1

•3.0V, 20 mA total Port 1 source current

•

❐5 mA strong drive mode on Ports 0 and 1

■

❐Eight unidirectional endpoints

❐One bidirectional control endpoint

❐USB 2.0 compliant

❐Dedicated 512 bytes buffer

❐No external crystal required

■Additional System Resources

❐Configurable communication speeds

❐I2C slave

•Selectable to 50 kHz, 100 kHz, or 400 kHz

•Implementation requires no clock stretching

•Implementation during sleep modes with less than 100 μA

•Hardware address detection

❐SPI master and SPI slave

•Configurable between 93.75 kHz and 12 MHz

❐Three

❐

❐Watchdog and sleep timers

❐Integrated supervisory circuit

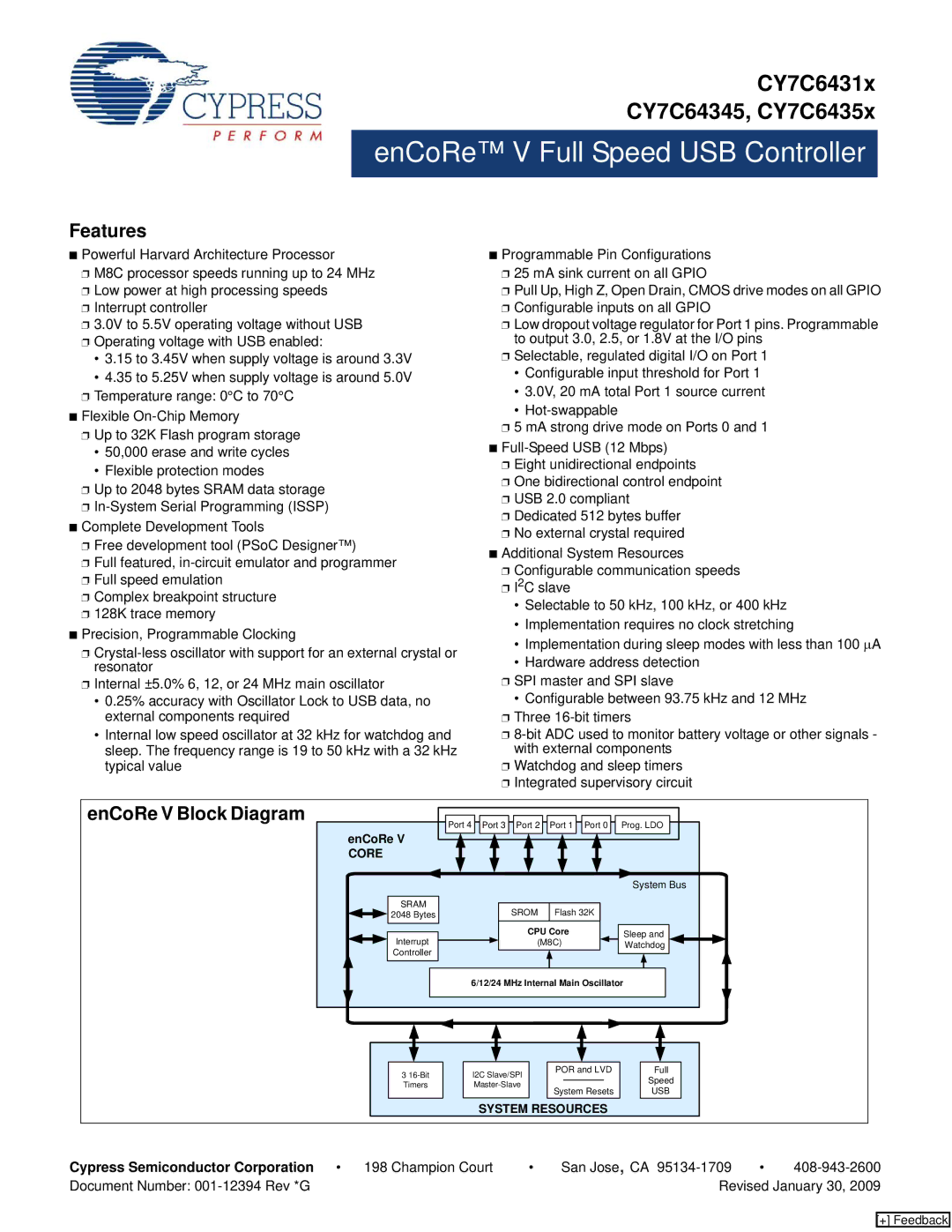

enCoRe V Block Diagram | Port 3 | Port 2 | Port 1 Port 0 | Prog. LDO |

Port 4 | ||||

enCoRe V |

|

|

|

|

CORE |

|

|

|

|

|

|

|

| System Bus |

SRAM |

| SROM | Flash 32K |

|

2048 Bytes |

|

| ||

Interrupt |

| CPU Core | Sleep and | |

| (M8C) | Watchdog | ||

Controller |

|

|

|

|

6/12/24 MHz Internal Main Oscillator | ||||

3

I2C Slave/SPI |

| POR and LVD | ||

|

|

|

| |

| System Resets | |||

|

| |||

SYSTEM RESOURCES

Full

Speed

USB

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised January 30, 2009 | ||

[+] Feedback