|

|

|

|

|

|

|

|

|

|

|

|

|

|

| STK17T88 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

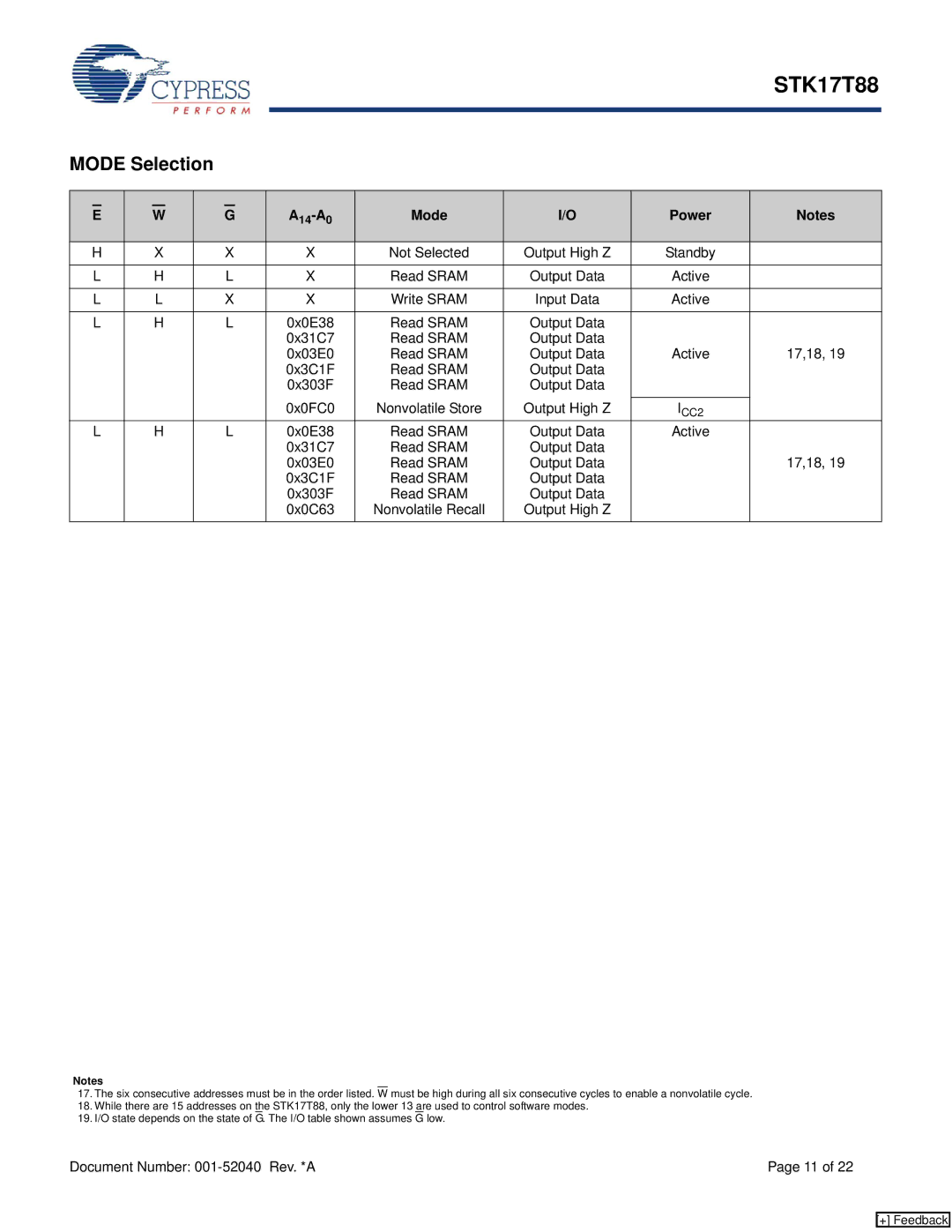

MODE Selection |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Mode | I/O | Power | Notes |

| E |

|

| W |

|

| G |

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

| X |

| X |

|

| X | Not Selected | Output High Z | Standby |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| L |

| H |

| L |

|

| X | Read SRAM | Output Data | Active |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| L |

| L |

| X |

|

| X | Write SRAM | Input Data | Active |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| L |

| H |

| L |

|

| 0x0E38 | Read SRAM | Output Data |

|

| |||

|

|

|

|

|

|

|

|

|

|

| 0x31C7 | Read SRAM | Output Data |

|

|

|

|

|

|

|

|

|

|

|

|

| 0x03E0 | Read SRAM | Output Data | Active | 17,18, 19 |

|

|

|

|

|

|

|

|

|

|

| 0x3C1F | Read SRAM | Output Data |

|

|

|

|

|

|

|

|

|

|

|

|

| 0x303F | Read SRAM | Output Data |

|

|

|

|

|

|

|

|

|

|

|

|

| 0x0FC0 | Nonvolatile Store | Output High Z | ICC2 |

|

| L |

| H |

| L |

|

| 0x0E38 | Read SRAM | Output Data | Active |

| |||

|

|

|

|

|

|

|

|

|

|

| 0x31C7 | Read SRAM | Output Data |

|

|

|

|

|

|

|

|

|

|

|

|

| 0x03E0 | Read SRAM | Output Data |

| 17,18, 19 |

|

|

|

|

|

|

|

|

|

|

| 0x3C1F | Read SRAM | Output Data |

|

|

|

|

|

|

|

|

|

|

|

|

| 0x303F | Read SRAM | Output Data |

|

|

|

|

|

|

|

|

|

|

|

|

| 0x0C63 | Nonvolatile Recall | Output High Z |

|

|

Notes

17.The six consecutive addresses must be in the order listed. W must be high during all six consecutive cycles to enable a nonvolatile cycle.

18.While there are 15 addresses on the STK17T88, only the lower 13 are used to control software modes.

19.I/O state depends on the state of G. The I/O table shown assumes G low.

Document Number: | Page 11 of 22 |

[+] Feedback