|

|

|

|

|

|

|

|

|

|

|

|

| STK17T88 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

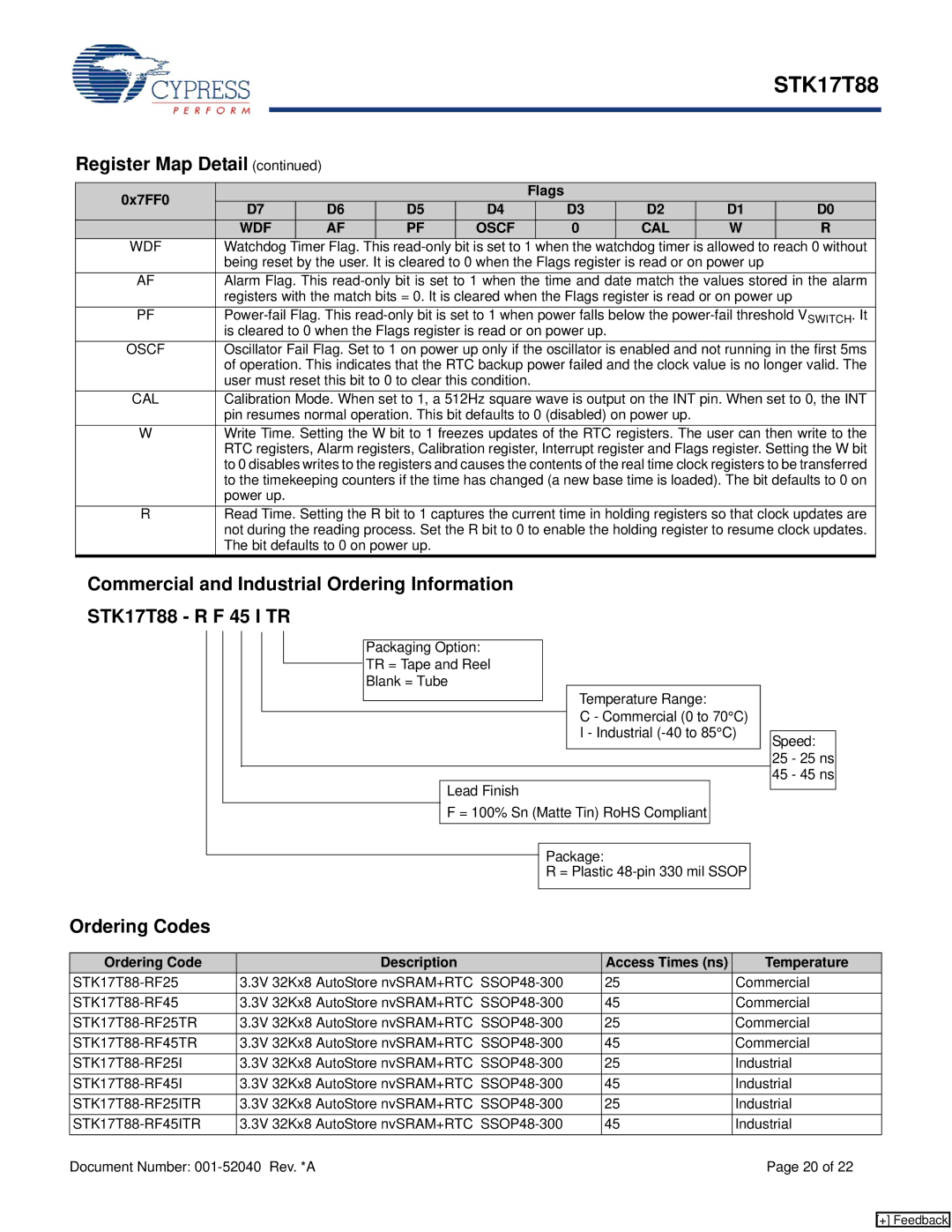

| Register Map Detail (continued) |

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 0x7FF0 |

|

|

|

|

|

| Flags |

|

|

|

|

|

| |

| D7 |

| D6 | D5 | D4 |

| D3 | D2 | D1 | D0 |

|

| |||

|

|

|

|

| |||||||||||

|

| WDF |

| AF | PF | OSCF |

| 0 | CAL | W | R |

|

| ||

| WDF | Watchdog | Timer Flag. This |

|

| ||||||||||

|

| being reset by the user. It is cleared to 0 when the Flags register is read or on power up |

|

|

| ||||||||||

| AF | Alarm Flag. This |

| ||||||||||||

|

| registers with the match bits = 0. It is cleared when the Flags register is read or on power up | |||||||||||||

| PF |

| |||||||||||||

|

| is cleared to 0 when the Flags register is read or on power up. |

|

|

|

|

| ||||||||

| OSCF | Oscillator Fail Flag. Set to 1 on power up only if the oscillator is enabled and not running in the first 5ms |

| ||||||||||||

|

| of operation. This indicates that the RTC backup power failed and the clock value is no longer valid. The | |||||||||||||

|

| user must reset this bit to 0 to clear this condition. |

|

|

|

|

|

| |||||||

| CAL | Calibration Mode. When set to 1, a 512Hz square wave is output on the INT pin. When set to 0, the INT |

| ||||||||||||

|

| pin resumes normal operation. This bit defaults to 0 (disabled) on power up. |

|

|

|

| |||||||||

WWrite Time. Setting the W bit to 1 freezes updates of the RTC registers. The user can then write to the RTC registers, Alarm registers, Calibration register, Interrupt register and Flags register. Setting the W bit to 0 disables writes to the registers and causes the contents of the real time clock registers to be transferred to the timekeeping counters if the time has changed (a new base time is loaded). The bit defaults to 0 on power up.

RRead Time. Setting the R bit to 1 captures the current time in holding registers so that clock updates are not during the reading process. Set the R bit to 0 to enable the holding register to resume clock updates. The bit defaults to 0 on power up.

Commercial and Industrial Ordering Information

STK17T88 - R F 45 I TR

Packaging Option:

TR = Tape and Reel

Blank = Tube

Temperature Range:

C - Commercial (0 to 70°C)

I - Industrial

Lead Finish

F = 100% Sn (Matte Tin) RoHS Compliant

Package:

R = Plastic

Ordering Codes

Speed:

25 - 25 ns

45 - 45 ns

Ordering Code | Description | Access Times (ns) | Temperature |

3.3V 32Kx8 AutoStore nvSRAM+RTC | 25 | Commercial | |

3.3V 32Kx8 AutoStore nvSRAM+RTC | 45 | Commercial | |

3.3V 32Kx8 AutoStore nvSRAM+RTC | 25 | Commercial | |

| 3.3V 32Kx8 AutoStore nvSRAM+RTC | 45 | Commercial |

3.3V 32Kx8 AutoStore nvSRAM+RTC | 25 | Industrial | |

3.3V 32Kx8 AutoStore nvSRAM+RTC | 45 | Industrial | |

3.3V 32Kx8 AutoStore nvSRAM+RTC | 25 | Industrial | |

| 3.3V 32Kx8 AutoStore nvSRAM+RTC | 45 | Industrial |

Document Number: |

| Page 20 of 22 | |

[+] Feedback