The integrated video subsystem supports all video graphics array (VGA) modes and is compliant with super video graphics array (SVGA) modes and Video Electronics Standards Association (VESA) 1.2. Some enhanced features include:

•Integrated video subsystem on chip, including 2D, 3D, and video port

•66 MHz AGP system bus interface with 2X and 4X

•Sideband signaling (some models only)

•Command list bus mastering support for fast 2D and 3D performance

•

•Plug and Play support

•4 MB dynamic display cache memory

•Advanced Power Management (APM) support

•Color space conversion

•Hardware scaling

The integrated graphics memory controller subsystem complys with the VESA Display Data Channel (DDC) 1.1 standard and uses DDC1 and DDC2B to determine optimal values during automatic minor detection.

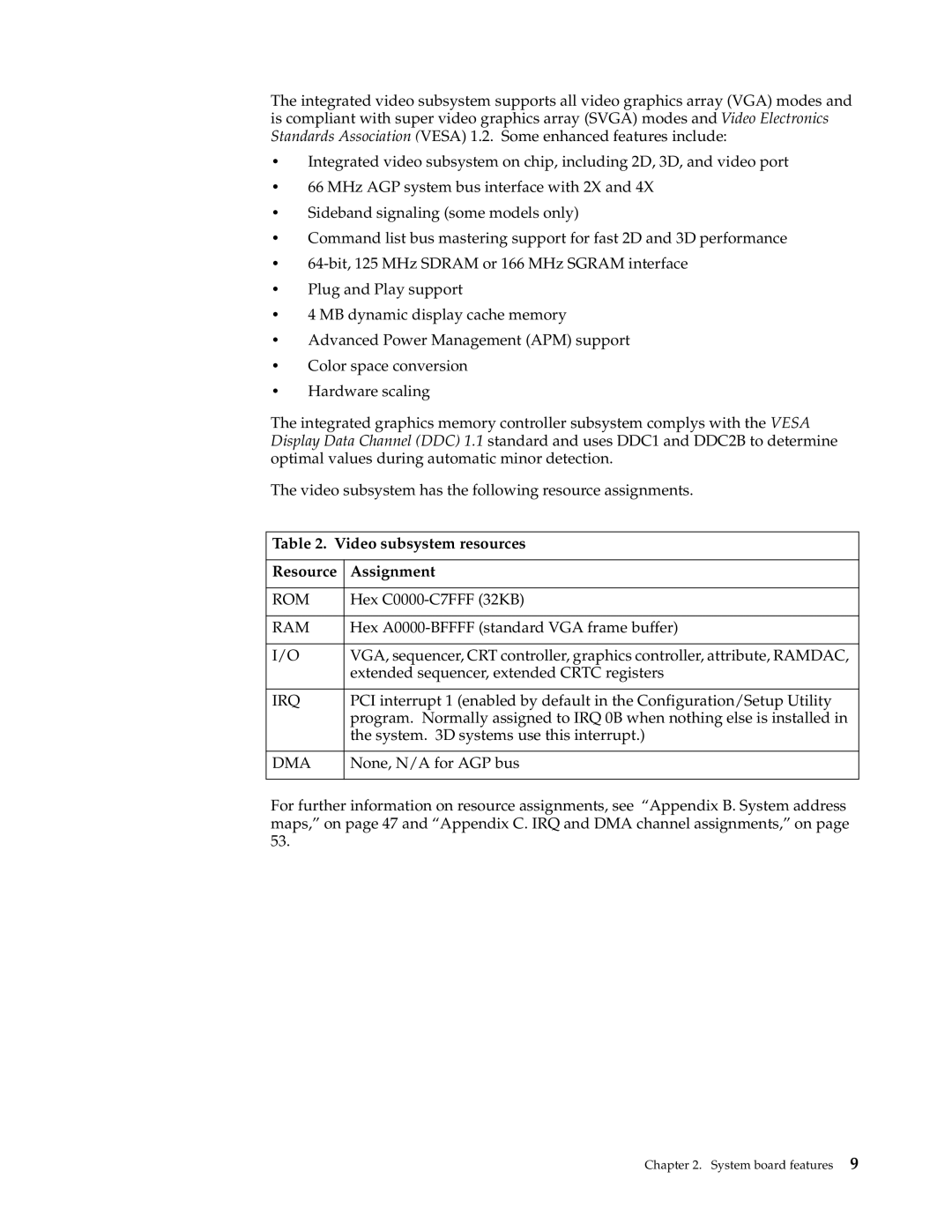

The video subsystem has the following resource assignments.

Table 2. Video subsystem resources

Resource | Assignment |

|

|

ROM | Hex |

|

|

RAM | Hex |

|

|

I/O | VGA, sequencer, CRT controller, graphics controller, attribute, RAMDAC, |

| extended sequencer, extended CRTC registers |

|

|

IRQ | PCI interrupt 1 (enabled by default in the Configuration/Setup Utility |

| program. Normally assigned to IRQ 0B when nothing else is installed in |

| the system. 3D systems use this interrupt.) |

|

|

DMA | None, N/A for AGP bus |

|

|

For further information on resource assignments, see “Appendix B. System address maps,” on page 47 and “Appendix C. IRQ and DMA channel assignments,” on page 53.

Chapter 2. System board features 9