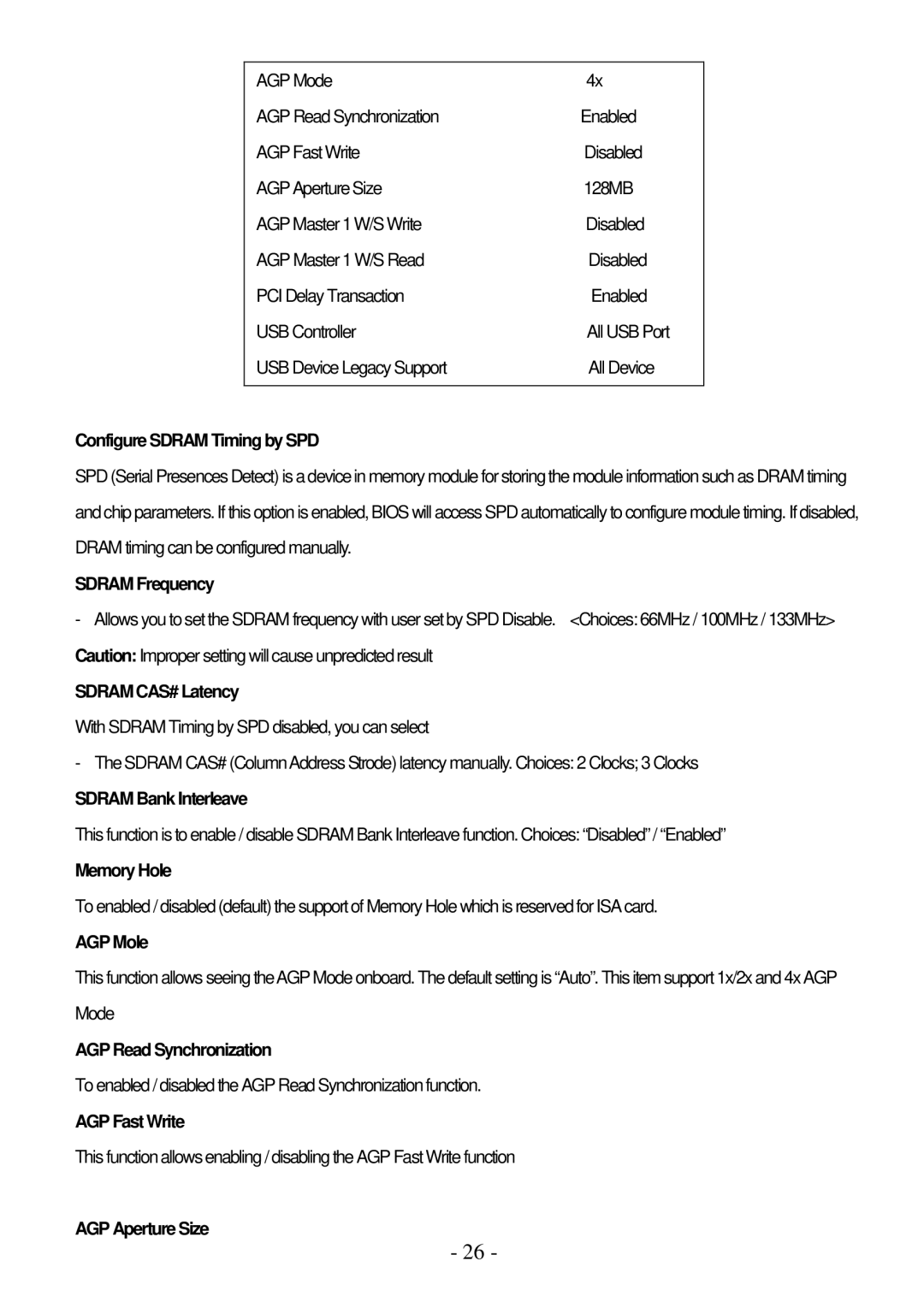

AGP Mode | 4x |

AGP Read Synchronization | Enabled |

AGP Fast Write | Disabled |

AGP Aperture Size | 128MB |

AGP Master 1 W/S Write | Disabled |

AGP Master 1 W/S Read | Disabled |

PCI Delay Transaction | Enabled |

USB Controller | All USB Port |

USB Device Legacy Support | All Device |

|

|

Configure SDRAM Timing by SPD

SPD (Serial Presences Detect) is a device in memory module for storing the module information such as DRAM timing and chip parameters. If this option is enabled, BIOS will access SPD automatically to configure module timing. If disabled, DRAM timing can be configured manually.

SDRAM Frequency

- Allows you to set the SDRAM frequency with user set by SPD Disable. <Choices: 66MHz / 100MHz / 133MHz>

Caution: Improper setting will cause unpredicted result

SDRAM CAS# Latency

With SDRAM Timing by SPD disabled, you can select

- The SDRAM CAS# (ColumnAddress Strode) latency manually. Choices: 2 Clocks; 3 Clocks

SDRAM Bank Interleave

This function is to enable / disable SDRAM Bank Interleave function. Choices: “Disabled”/ “Enabled”

Memory Hole

To enabled / disabled (default) the support of Memory Hole which is reserved for ISA card.

AGP Mole

This function allows seeing theAGP Mode onboard. The default setting is “Auto”. This item support 1x/2x and 4x AGP Mode

AGP Read Synchronization

To enabled / disabled the AGP Read Synchronization function.

AGP Fast Write

This function allows enabling / disabling the AGP Fast Write function

AGP Aperture Size

- 26 -