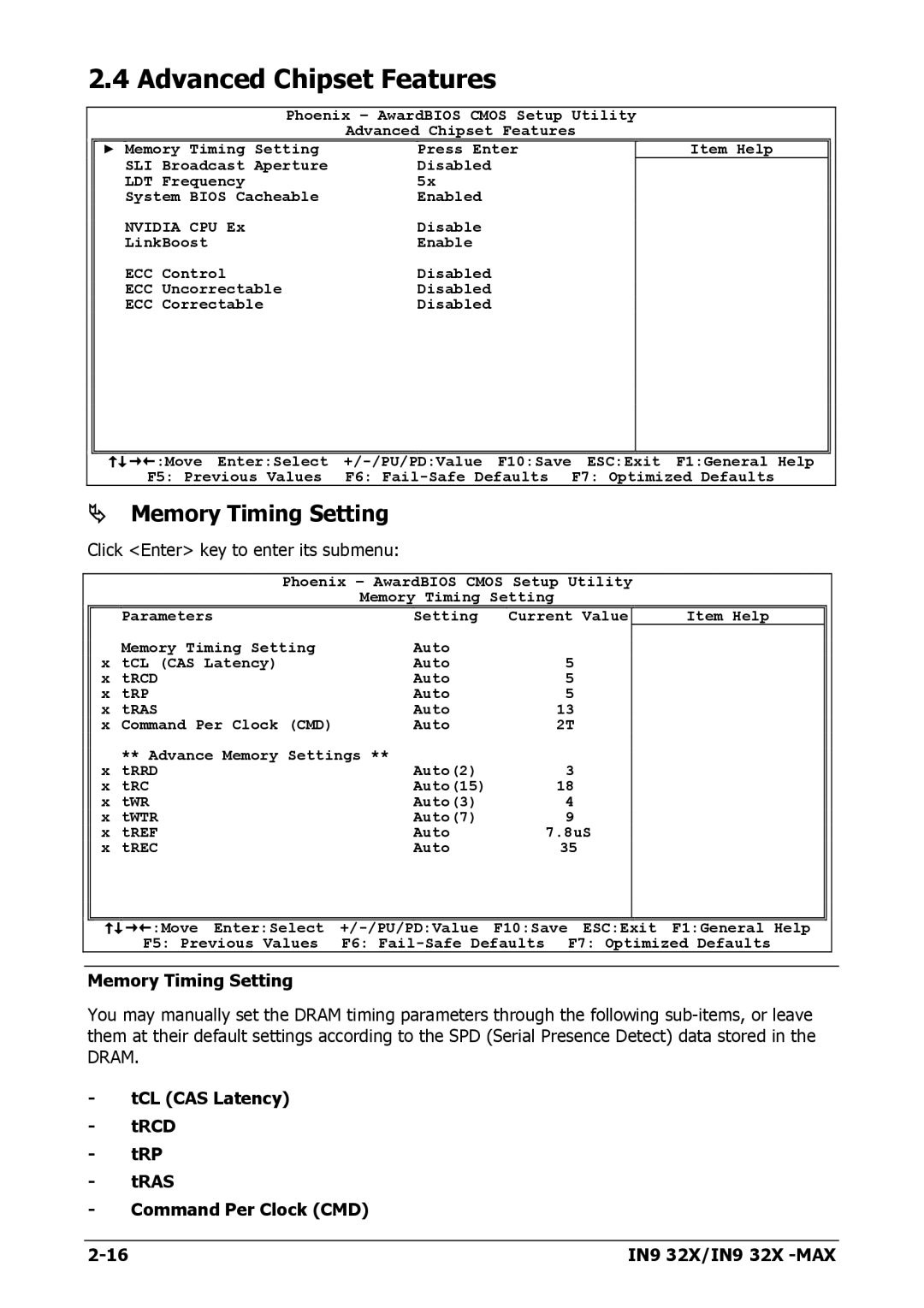

2.4 Advanced Chipset Features

Phoenix – AwardBIOS CMOS Setup Utility

Advanced Chipset Features

► Memory Timing Setting | Press Enter |

| Item Help |

SLI Broadcast Aperture | Disabled |

|

|

LDT Frequency | 5x |

|

|

System BIOS Cacheable | Enabled |

|

|

NVIDIA CPU Ex | Disable |

|

|

LinkBoost | Enable |

|

|

ECC Control | Disabled |

|

|

ECC Uncorrectable | Disabled |

|

|

ECC Correctable | Disabled |

|

|

|

|

| |

:Move Enter:Select | |||

F5: Previous Values | F6: | F7: Optimized Defaults | |

Memory Timing Setting

Click <Enter> key to enter its submenu:

Phoenix – AwardBIOS CMOS Setup Utility

Memory Timing Setting

|

|

|

|

|

| Parameters | Setting | Current Value | Item Help |

x | Memory Timing Setting | Auto | 5 |

|

tCL (CAS Latency) | Auto |

| ||

x | tRCD | Auto | 5 |

|

x | tRP | Auto | 5 |

|

x | tRAS | Auto | 13 |

|

x Command Per Clock (CMD) | Auto | 2T |

| |

x | ** Advance Memory Settings ** | 3 |

| |

tRRD | Auto(2) |

| ||

x | tRC | Auto(15) | 18 |

|

x | tWR | Auto(3) | 4 |

|

x | tWTR | Auto(7) | 9 |

|

x | tREF | Auto | 7.8uS |

|

x | tREC | Auto | 35 |

|

|

|

| ||

:Move Enter:Select | ||||

| F5: Previous Values | F6: | ||

Memory Timing Setting

You may manually set the DRAM timing parameters through the following

-tCL (CAS Latency)

-tRCD

-tRP

-tRAS

-Command Per Clock (CMD)

IN9 32X/IN9 32X |