1 | 2 | 3 | 4 |

A

|

|

|

| VDD | 1 | |||||

|

|

| RSF0 |

| ||||||

| 2 | |||||||||

|

|

|

| GND |

| |||||

| 3 | |||||||||

|

| RCLK0 |

| |||||||

| 4 | |||||||||

|

|

| DR0A |

| ||||||

| 5 | |||||||||

|

|

| DR0B |

| ||||||

| 6 | |||||||||

|

|

| TFS0 |

| ||||||

| 7 | |||||||||

|

| TCLK0 |

| |||||||

| 8 | |||||||||

|

|

|

| VDD |

| |||||

| 9 | |||||||||

|

|

|

| GND |

| |||||

| 10 | |||||||||

|

|

| DT0A |

| ||||||

| 11 | |||||||||

|

|

| DT0B |

| ||||||

| 12 | |||||||||

|

|

| RFS1 |

| ||||||

| 13 | |||||||||

|

|

|

| GND |

| |||||

| 14 | |||||||||

|

| RCLK1 |

| |||||||

| 15 | |||||||||

|

|

| DR1A |

| ||||||

| 16 | |||||||||

|

|

| DR1B |

| ||||||

| 17 | |||||||||

|

|

| TFS1 |

| ||||||

| 18 | |||||||||

B |

| TCLK1 |

| |||||||

19 | ||||||||||

|

|

| VDD |

| ||||||

|

|

|

| 20 | ||||||

|

|

|

| VDD |

| |||||

| 21 | |||||||||

|

|

| DT1A |

| ||||||

| 22 | |||||||||

|

|

| DT1B |

| ||||||

| 23 | |||||||||

| PWM EVENT1 |

| ||||||||

| 24 | |||||||||

|

|

|

| GND |

| |||||

| 25 | |||||||||

| PWM EVENT0 |

| ||||||||

| 26 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| BR | 1 | 27 | ||

|

|

|

|

| BR2 | 28 | ||||

|

|

|

| VDD |

| |||||

| 29 | |||||||||

|

| CLKIN |

| |||||||

| 30 | |||||||||

|

|

| XTAL |

| ||||||

| 31 | |||||||||

|

|

|

| VDD |

| |||||

| 32 | |||||||||

|

|

|

| GND |

| |||||

| 33 | |||||||||

| SDCLK1 |

| ||||||||

| 34 | |||||||||

|

|

|

| GND |

| |||||

| 35 | |||||||||

|

|

|

| VDD |

| |||||

| 36 | |||||||||

| SDCLK0 |

| ||||||||

| 37 | |||||||||

|

|

|

|

|

|

|

|

|

| |

|

| DMAR1 |

| 38 | ||||||

|

|

|

|

|

|

|

|

|

|

|

C |

| DMAR2 |

| 39 | ||||||

|

|

|

|

|

|

|

|

| ||

|

|

|

| HBR |

| 40 | ||||

|

|

|

| GND | 41 | |||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

| RAS |

| 42 | |||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

| CAS |

| 43 | |||

|

|

|

|

|

|

|

|

|

| |

|

|

| SDWE |

|

| 44 | ||||

|

|

|

| VDD | 45 | |||||

|

|

| DQM |

| ||||||

| 46 | |||||||||

|

| SDCKE |

| |||||||

| 47 | |||||||||

|

| SDA10 |

| |||||||

| 48 | |||||||||

|

|

|

| GND |

| |||||

| 49 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DMAG | 1 | 50 | ||||||

| DMAG2 |

| ||||||||

| 51 | |||||||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

| HBG |

|

| 52 | |||

D

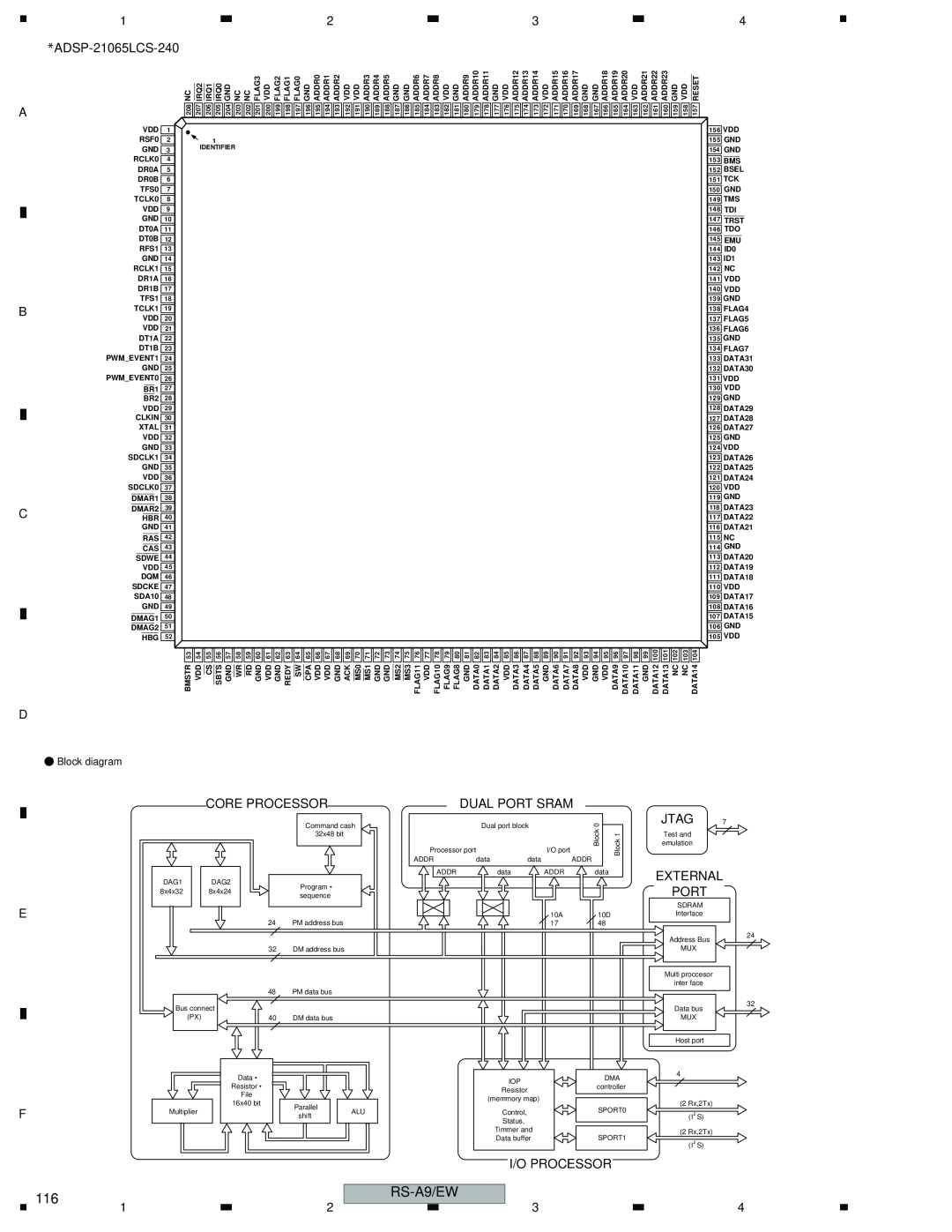

-Block diagram

NC |

| IRQ2 |

| IRQ1 |

| IRQ0 | GND | NC | NC | FLAG3 | VDD | FLAG2 | FLAG1 | FLAG0 | GND | ADDR0 | ADDR1 | ADDR2 | VDD | VDD | ADDR3 | ADDR4 | ADDR5 | GND | GND | ADDR6 | ADDR7 | ADDR8 | VDD | GND | ADDR9 | ADDR10 | ADDR11 | GND | VDD | ADDR12 | ADDR13 | ADDR14 | VDD | ADDR15 | ADDR16 | ADDR17 | GND | GND | ADDR18 | ADDR19 | ADDR20 | VDD | ADDR21 | ADDR22 | ADDR23 | GND | VDD |

| RESET |

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

208 |

| 207 |

| 206 |

| 205 | 204 | 203 | 202 | 201 | 200 | 199 | 198 | 197 | 196 | 195 | 194 | 193 | 192 | 191 | 190 | 189 | 188 | 187 | 186 | 185 | 184 | 183 | 182 | 181 | 180 | 179 | 178 | 177 | 176 | 175 | 174 | 173 | 172 | 171 | 170 | 169 | 168 | 167 | 166 | 165 | 164 | 163 | 162 | 161 | 160 | 159 | 158 |

| 157 |

|

|

|

|

| 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

IDENTIFIER

53 | 54 |

| 55 |

| 56 | 57 |

| 58 | 59 | 60 | 61 | 62 | 63 | 64 |

| 65 | 66 | 67 | 68 | 69 | 70 | 71 | 72 | 73 |

| 74 | 75 | 76 | 77 | 78 | 79 | 80 | 81 | 82 | 83 | 84 | 85 | 86 | 87 | 88 | 89 | 90 | 91 | 92 | 93 | 94 | 95 | 96 | 97 | 98 | 99 | 100 | 101 | 102 | 103 | 104 | |||||

BMSTR | VDD |

| CS |

| SBTS | GND |

| WR |

| RD | GND | VDD | GND | REDY |

| SW |

| CPA | VDD | VDD | GND | ACK |

| MS0 |

| MS1 | GND | GND |

| MS2 |

| MS3 | FLAG11 | VDD | FLAG10 | FLAG9 | FLAG8 | GND | DATA0 | DATA1 | DATA2 | VDD | DATA3 | DATA4 | DATA5 | GND | DATA6 | DATA7 | DATA8 | VDD | GND | VDD | DATA9 | DATA10 | DATA11 | GND | DATA12 | DATA13 | NC | NC | DATA14 |

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

156VDD

155GND

154GND

153BMS

152BSEL

151TCK

150GND

149TMS

148TDI

147TRST

146TDO

145EMU

144ID0

143ID1

142NC

141VDD

140VDD

139GND

138FLAG4

137FLAG5

136FLAG6

135GND

134FLAG7

133DATA31

132DATA30

131VDD

130VDD

129GND

128DATA29

127DATA28

126DATA27

125GND

124VDD

123DATA26

122DATA25

121DATA24

120VDD

119GND

118DATA23

117DATA22

116DATA21

115NC

114GND

113DATA20

112DATA19

111DATA18

110VDD

109DATA17

108DATA16

107DATA15

106GND

105VDD

| CORE PROCESSOR |

| Command cash |

| 32x48 bit |

DAG1 | DAG2 |

| Program • |

DUAL PORT SRAM

| Dual port block |

| 0 |

| |

|

| Block |

| ||

Processor port |

|

| I/O port | Block 1 | |

ADDR | data | data |

| ||

| ADDR |

| |||

ADDR |

| data | ADDR | data |

|

JTAG 7

Test and

emulation

EXTERNAL

8x4x32 | 8x4x24 | sequence |

|

| |

E | 24 | PM address bus |

| ||

| 32 | DM address bus |

10A | 10D |

17 | 48 |

PORT

SDRAM

Interface

Address Bus

MUX

24

Multi proccesor

inter face

| 48 | PM data bus |

Bus connect |

|

|

(PX) | 40 | DM data bus |

Data bus

MUX

32

|

| Data • |

|

|

|

| Resistor • |

|

|

|

| File |

|

|

F |

| 16x40 bit | Parallel |

|

Multiplier |

| ALU | ||

| shift | |||

|

|

|

116 | 2 |

1 |

IOP | DMA | |

controller | ||

Resistor | ||

| ||

(memmory map) |

| |

Control, | SPORT0 | |

| ||

Status, |

| |

Timmer and |

| |

Data buffer | SPORT1 |

I/O PROCESSOR

3

Host port

4

(2 Rx,2Tx)

(I2 S)

(2 Rx,2Tx)

(I2 S)

4