•DEV is reserved.

•

•LBA is to select the Logical Block Addressing Mode. When LBA=0, disk addressing is by CHS mode.

•When LBA=1, disk addressing is by LBA mode. This bit was set to zero when the ATA drive didn’t support LBA mode.

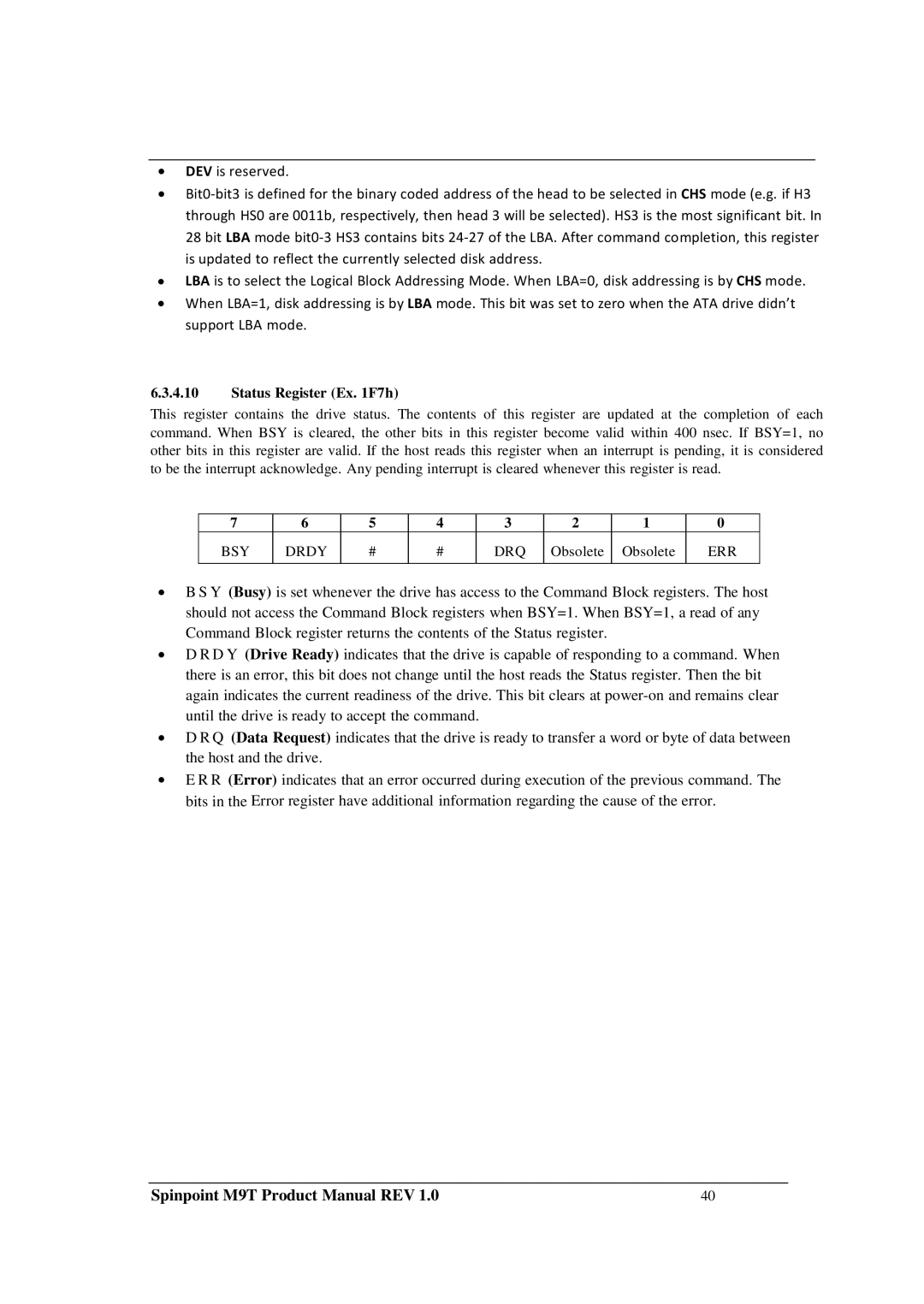

6.3.4.10Status Register (Ex. 1F7h)

This register contains the drive status. The contents of this register are updated at the completion of each command. When BSY is cleared, the other bits in this register become valid within 400 nsec. If BSY=1, no other bits in this register are valid. If the host reads this register when an interrupt is pending, it is considered to be the interrupt acknowledge. Any pending interrupt is cleared whenever this register is read.

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

BSY | DRDY | # | # | DRQ | Obsolete | Obsolete | ERR |

|

|

|

|

|

|

|

|

•B S Y (Busy) is set whenever the drive has access to the Command Block registers. The host should not access the Command Block registers when BSY=1. When BSY=1, a read of any Command Block register returns the contents of the Status register.

•D R D Y (Drive Ready) indicates that the drive is capable of responding to a command. When there is an error, this bit does not change until the host reads the Status register. Then the bit again indicates the current readiness of the drive. This bit clears at

•D R Q (Data Request) indicates that the drive is ready to transfer a word or byte of data between the host and the drive.

•E R R (Error) indicates that an error occurred during execution of the previous command. The bits in the Error register have additional information regarding the cause of the error.

Spinpoint M9T Product Manual REV 1.0 | 40 |