Electronic Tuning ETR Controllers

LC723780 Series

Overview

The LC723780 series are

In addition to a rich set of table reference instructions to take advantage of the large ROM capacity, these devices also feature an improved interrupt system for direct control of the CD mechanism and the CD DSP, support for RDS products, and powerful communications for use within the end product and with external systems as well.

In car audio applications in particular, these communication functions allow a reduction in the number connecting wires between the front panel circuit board and the main system circuit board.

Functions

■ROM/RAM: 40 KB/2 KB (LC723781) 48 KB/2 KB (LC723782) 64 KB/4 KB (LC723783) 96 KB/6 KB (LC723784)

128 KB/8 KB (LC723785)

■Cycle time: 1.33 ∝s/833 ns (all instructions are one word) at 4.5 MHz/7.2 MHz

■Serial I/O: Three channels (supports

■Multiple interrupts: 16 levels

■A/D converter:

■PLL block: Dead zone control, unlocked state detection circuit

■QTP version: LC72F3781

■Package: QIP100E (14 ![]() 20 mm)

20 mm)

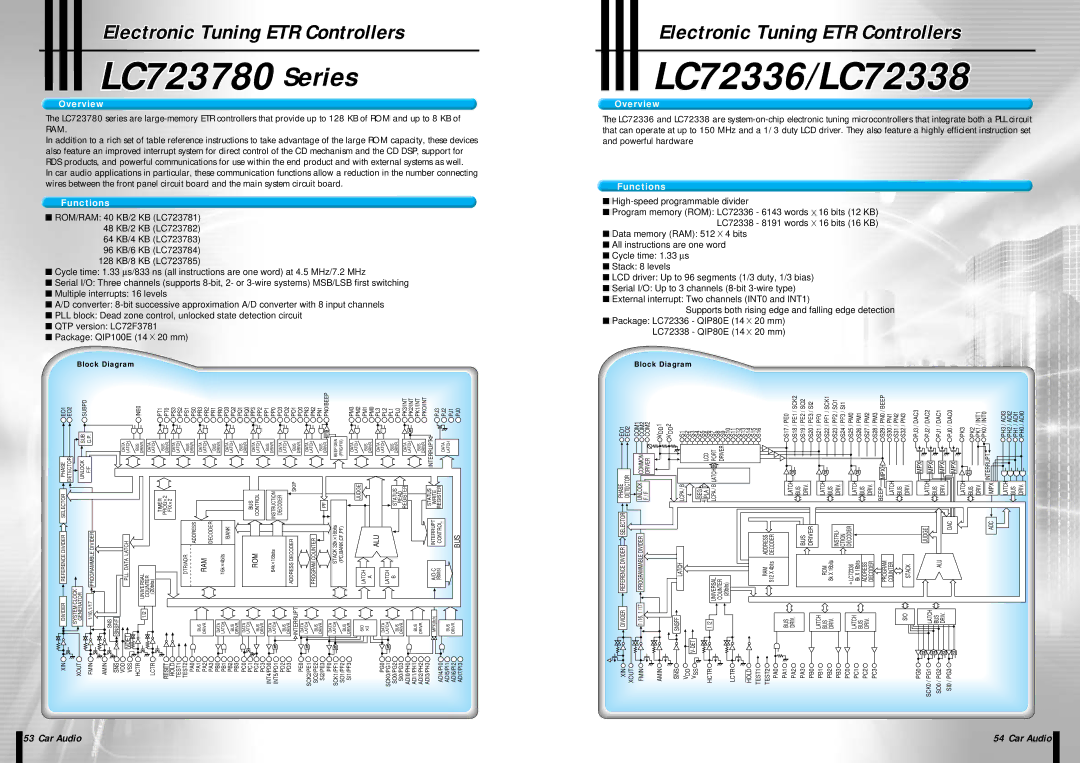

Block Diagram

Electronic Tuninguning ETRETR ControllersControllers

LC72336/LC723386/LC72338

Overview

The LC72336 and LC72338 are

Functions

■

■Program memory (ROM): LC72336 - 6143 words ![]() 16 bits (12 KB) LC72338 - 8191 words

16 bits (12 KB) LC72338 - 8191 words ![]() 16 bits (16 KB)

16 bits (16 KB)

■Data memory (RAM): 512 ![]() 4 bits

4 bits

■All instructions are one word

■Cycle time: 1.33 ∝s

■Stack: 8 levels

■LCD driver: Up to 96 segments (1/3 duty, 1/3 bias)

■Serial I/O: Up to 3 channels

■External interrupt: Two channels (INT0 and INT1)

Supports both rising edge and falling edge detection

■Package: LC72336 - QIP80E (14 ![]() 20 mm) LC72338 - QIP80E (14

20 mm) LC72338 - QIP80E (14 ![]() 20 mm)

20 mm)

Block Diagram

EO1 | EO2 |

| SUBPD |

|

|

|

| INE0 |

|

|

| PT1 |

| PT0 | PS3 | PS2 | PS1 | PS0 | PR3 | PR2 | PR1 | PR0 | PQ3 | PQ2 | PQ1 | PQ0 | PP3 | PP2 | PP1 | PP0 | PO3 | PO2 | PO1 |

| PO0 | PN3 | PN2 | PN1 | PN0/BEEP |

|

| PM3 | PM2 | PM1 | PM0 | PL3 | PL2 | PL1 | PL0 | PK3/INT | PK2/INT | PK1/INT | PKO/INT | PJ3 | PJ2 | PJ1 | PJ0 | |||||||||||

|

|

| SUB | C.P. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MPX | BEEP GEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DETECTOR |

|

| DATA | LATCH | BUS | DRIVR. | DATA | LATCH | BUS | DRIVR. | DATA | LATCH | BUS | DRIVR. | DATA | LATCH |

| BUS | DRIVR. |

|

| DATA | LATCH |

|

| BUS | DRIVR. | DATA | LATCH |

| BUS | DRIVR. | DATA | LATCH |

| BUS | DRIVR. | DATA | LATCH |

| BUS | DRIVR. | (PRG/FIX) | DATA | LATCH | BUS | DRIVR. | DATA | LATCH | BUS | DRIVR. | DATA | LATCH |

| BUS | DRIVR. | INTERRUPT | DATA | LATCH |

|

| ||||||

SELECTOR PHASE | CLOCKSYSTEM | UNLOCK | F/F | SNS | SNSF/F | VDET |

| 1/2 |

| (20bits) | TIMER | PROG 2 FIX 2 |

| DTR/ADR | ADDRESS | DRIVR.BUSRAM | DECODER | DATA | LATCH16k 4bits | BANK | BUS | DRIVR. |

| BUS | CONTROL | .DRIVR |

| INSTRUCTION | DECODER | BUS | DRIVR. | SKIP |

| DATA | LATCH | BUS | PF | LATCH STACK 32k 16bits | BUS | DRIVR. | JUDGE |

| ALU |

| STATUS READ REGISTER |

| BUS | DRIVR. | STATUS WRITE REGISTER |

| BUS | DRIVR. | ||||||||||||||||

REFERENCEDIVIDER DIVIDER |

| GENERATOR | 1/16,1/17 |

|

|

|

|

|

|

| DATA LATCH |

| BUS | DATA LATCH |

| INTERRUPT | DRIVR. | DATA | SIO 3 | DATA LATCHLATCH | BUS | DRIVR. |

|

| ||||||||||||||||||||||||||||||||||||||||||||

|

|

|

| PROGRAMMBLEDIVIDER |

| LATCHDATAPLL |

| UNIVERSAL COUNTER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ROM |

|

| 16bits64k |

|

| DECODERADDRESS |

|

|

| PROGRAMCOUNTER |

|

|

|

| (PC,BANK,CF,PF) |

|

| LATCH | A |

|

| B |

|

|

|

|

| CONTROL |

|

|

| BUS | |||||

EO1 EO2 | COM1 COM2 COM2 | V | V | |

|

|

| 1 | 2 |

|

|

| DD | DD |

PHASE DETECTOR | COMMON | DRIVER |

|

|

UNLOCK | F / F |

|

| |

SELECTOR | PROGRAMMABLE DIVIDER |

|

|

|

REFERENCE DIVIDER |

|

|

| |

DIVIDER | 1 /16, 1 /17 |

|

|

|

S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 S16 |

|

| S17 / PE0 | S18 / PE1 / SCK2 | S19 / PE2 / SO2 | S20 / PE3 / SI2 | S21 / PF0 S22 / PF1 / SCK1 | S23 / PF2 / SO1 | S24 / PF3 / SI1 | S25 / PM0 | S26 / PM1 | S27 / PM2 S28 / PM3 | S29 / PN0 / BEEP | S30 / PN1 | S31 / PN2 S32 / PN3 | |||||

| LCD | PORT | DRIVER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LCPA/ B 4 |

| 96 |

|

|

| LATCH | BUS | DRIV. |

| LATCH | BUS | DRIV. |

| LATCH BUS | DRIV. | MPX | LATCH BUS DRIV. | |||

4 | LCPA/LATCHB |

|

|

|

|

| BEEP | |||||||||||||

| 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SEG PLA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ADDRESS | DECODER |

|

| BUS | DRIVER |

|

| INSTRU- | CTION | DECODER |

|

|

|

|

|

|

LATCH |

| UNIVERSAL | COUNTER (20bits) | RAM | 512 X 4bits |

|

|

|

| ROM | 8k X 16bits |

| ∗ LC72336 | 6k X 16bits | ADDRESS | DECODER | PROGRAM | COUNTER | STACK | |

PJ3 / DAC3 | PJ2 / DAC2 |

| PJ1 / DAC1 | PJ0 / DAC0 | PK3 | PK2 PK1 / INT1 PK0 / INT0 | PH3 / ADI3 PH2 / ADI2 PH1 / ADI1 PH0 / ADI0 | |||||

MPX | MPX |

| MPX | MPX |

|

|

| INTERRUPT |

|

|

| |

| LATCH | BUS | DRIV. |

| LATCH | BUS | DRIV. | MPX | LATCH | BUS | DRIV. | |

| JUDGE |

|

|

| DAC |

|

|

| ADC |

|

|

|

|

|

| ALU |

|

|

|

|

|

|

|

| |

SNSFF | 1 /2 | BUS DRIV. | LATCH BUS DRIV. | LATCH BUS DRIV. | SIO | LATCH BUS DRIV. |

|

|

|

|

|

|

XIN | XOUT | FMIN | AMIN |

| SNS VDD VSS HCTR | LCTR | RESET |

| HOLD TEST1 TEST2 PA0 PA1 PA2 PA3 PB0 PB1 PB2 PB3 PC0 PC1 PC2 PC3 INT4/PD0 INT5/PD1 PD2 PD3 | PE0 SCK2/PE1 SO2/PE2 SI2/PE3 PF0 SCK1/PF1 SO1/PF2 SI1/PF3 | PG0 SCK0/PG1 SO0/PG2 SI0/PG3 ADI0/PH0 ADI1/PH1 ADI2/PH2 ADI3/PH3 | ADI4/PI0 ADI5/PI1 ADI6/PI2 ADI7/PI3 |

|

| |||||||||||

|

|

|

|

|

|

|

|

XIN XOUT | FMIN | AMIN | SNS | V | V | HCTR | LCTR | HOLD TEST1 | TEST2 PA0 PA1 PA2 PA3 PB0 PB1 PB2 PB3 PC0 PC1 PC2 PC3 | PG0 | SCK0/ PG1 | SO0/ PG2 | SI0/ PG3 |

|

|

|

| DD | SS |

|

|

|

|

|

|

|

|

| 53 Car Audio | 54 Car Audio |

|

|

|