Car Audio DSP

LC75010W0W

Overview

The LC75010W is a

Features

■ Analog source selector | ■ Analog characteristic (S/N) | ||||||

◆Single input: 3 systems, differential input: 1 system | ◆Typ. 90 dB (Note) | ||||||

■ A/D | ■ Analog characteristic (dynamic range) | ||||||

◆Stereo: 1 system | ◆Typ. 90 dB (Note) | ||||||

■ DSP core | ■ Analog characteristic (THD + N) | ||||||

◆Typ. | |||||||

■ D/A | ■ Power supply voltage (5 V) | ||||||

◆4 systems | ◆4.75 V to 5.25 V | ||||||

■ Analog volume | ■ Power supply voltage (3.3 V) | ||||||

◆4 systems | ◆3.0 V to 3.6 V | ||||||

■ Microcontroller interface | ■ Operating ambient temperature | ||||||

◆1 system (SANYO Electric original format) | |||||||

(CCB: Computer Control Bus) | ■ Package: SQFP100 (14 14) | ||||||

| Note: Analog characteristics are according to SANYO Electric measurement conditions. | ||||||

| CCB is a SANYO’s original bus format and all the |

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

| ||||

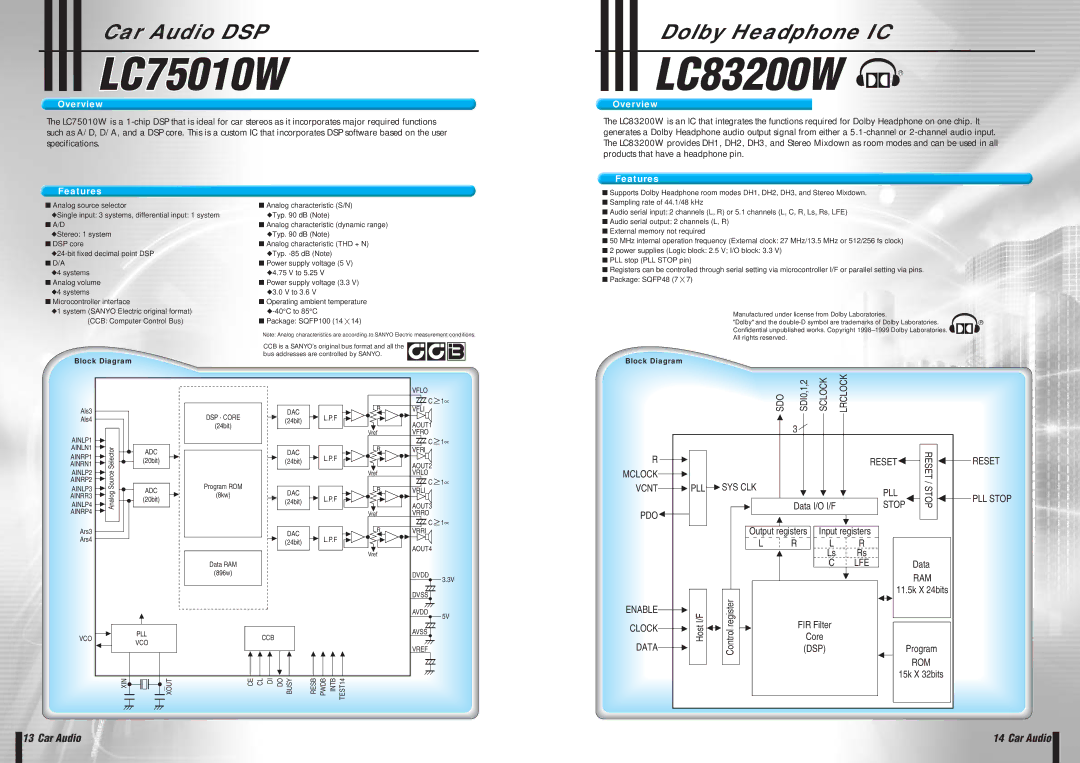

Block Diagram | bus addresses are controlled by SANYO. | ||||||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| VFLO |

|

|

|

|

|

|

|

|

|

|

| R | C | 1∝ |

Als3 |

|

|

|

|

|

| DAC |

|

| VFLI |

| |

|

| DSP · CORE |

|

|

|

| L.P.F |

|

| |||

Als4 |

|

|

|

|

| (24bit) |

|

| AOUT1 |

| ||

|

|

| (24bit) |

|

|

|

|

|

|

|

| |

AINLP1 |

|

|

|

|

|

|

|

|

| Vref | VFRO |

|

|

|

|

|

|

|

|

|

|

| C | ∝ | |

AINLN1 |

|

|

|

|

|

|

|

|

| R | 1 | |

Selector | ADC |

|

|

|

| DAC |

|

| VFRI |

| ||

AINRP1 |

|

|

|

|

| L.P.F |

|

|

| |||

(20bit) |

|

|

|

| (24bit) |

|

|

|

| |||

AINRN1 |

|

|

|

|

|

|

| AOUT2 |

| |||

AINLP2 | Source |

|

|

|

|

|

|

|

| Vref | VRLO |

|

AINRP2 |

| Program ROM |

|

|

|

|

|

|

| C | 1∝ | |

AINLP3 | ADC |

|

|

|

|

|

| R | ||||

Analog | (8kw) |

|

|

| DAC |

|

| VRLI |

| |||

AINRR3 | (20bit) |

|

|

|

| L.P.F |

|

|

| |||

AINLP4 |

|

|

|

| (24bit) |

|

| AOUT3 |

| |||

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |||

AINRP4 |

|

|

|

|

|

|

|

|

| Vref | VRRO |

|

|

|

|

|

|

|

|

|

|

| R | C | 1∝ |

Ars3 |

|

|

|

|

|

| DAC |

|

| VRRI |

| |

|

|

|

|

|

|

| L.P.F |

|

| |||

Ars4 |

|

|

|

|

|

| (24bit) |

|

|

|

| |

|

|

|

|

|

|

|

|

|

| AOUT4 |

| |

|

|

|

|

|

|

|

|

|

| Vref |

| |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| Data RAM |

|

|

|

|

|

|

|

|

|

|

|

| (896w) |

|

|

|

|

|

|

| DVDD | 3.3V |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| DVSS |

|

|

|

|

|

|

|

|

|

|

|

| AVDD | 5V |

|

|

|

|

|

|

|

|

|

|

|

| |

VCO |

| PLL |

|

| CCB |

|

|

|

|

| AVSS |

|

|

|

|

|

|

|

|

|

|

| |||

| VCO |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| VREF |

| |

|

|

|

|

|

|

|

|

|

|

|

| |

| XIN |

| XOUT | CE | CL DI | DO | BUSY | RESB | PWDB INTB | TEST14 |

|

|

Dolby Headphone IC

LC83200W0W

R

R

Overview

The LC83200W is an IC that integrates the functions required for Dolby Headphone on one chip. It generates a Dolby Headphone audio output signal from either a

Features

■Supports Dolby Headphone room modes DH1, DH2, DH3, and Stereo Mixdown.

■Sampling rate of 44.1/48 kHz

■Audio serial input: 2 channels (L, R) or 5.1 channels (L, C, R, Ls, Rs, LFE)

■Audio serial output: 2 channels (L, R)

■External memory not required

■50 MHz internal operation frequency (External clock: 27 MHz/13.5 MHz or 512/256 fs clock)

■2 power supplies (Logic block: 2.5 V; I/O block: 3.3 V)

■PLL stop (PLL STOP pin)

■Registers can be controlled through serial setting via microcontroller I/F or parallel setting via pins.

■Package: SQFP48 (7 ![]() 7)

7)

Manufactured under license from Dolby Laboratories. |

|

"Dolby" and the | R |

Confidential unpublished works. Copyright |

|

All rights reserved. |

|

Block Diagram

|

| SDO | SDI0,1,2 | SCLOCK | LRCLOCK |

|

|

|

|

| 3 |

|

|

|

|

R |

|

|

|

| RESET | RESET | RESET |

MCLOCK |

|

|

|

|

|

| |

VCNT | PLL | SYS CLK |

|

|

| / |

|

|

| PLL | STOP | PLL STOP | |||

|

|

|

|

| |||

|

|

| Data I/O I/F | STOP | |||

PDO |

|

|

| ||||

|

|

|

|

|

|

| |

|

| Output registers | Input registers |

|

| ||

|

| L | R | L | R |

|

|

|

|

|

| Ls | Rs |

|

|

|

|

|

| C | LFE | Data |

|

|

|

|

|

|

| RAM |

|

|

|

|

|

| 11.5k X 24bits |

| |

ENABLE | Host I/F | Control register |

|

|

|

|

|

CLOCK | FIR Filter |

|

|

| |||

Core |

|

|

| ||||

DATA |

|

|

| ||||

(DSP) |

| Program |

| ||||

|

|

|

| ROM |

| ||

|

|

|

|

|

|

| |

|

|

|

|

| 15k X 32bits |

| |

| 13 Car Audio | 14 Car Audio |

|

|

|