5KW specifications

The TDK 5KW is a cutting-edge power supply solution designed to deliver high performance and efficiency in a compact form. This robust unit is engineered for various applications, including industrial automation, telecommunications, and renewable energy systems. With a focus on reliability and durability, the TDK 5KW is an excellent choice for users seeking a dependable power source.One of the standout features of the TDK 5KW is its advanced power conversion technology. It utilizes a high-frequency switching technique that allows for superior efficiency, minimizing energy loss and reducing heat generation. By operating at high efficiency levels, the TDK 5KW helps lower operational costs while contributing to a greener environment.

The power supply is equipped with a wide input voltage range, making it suitable for global applications. It can accept input voltages from 90 to 264 VAC, ensuring versatility and compatibility with various electrical systems. This feature also enhances its usability in different geographic regions without the need for additional transformers or converters.

Another significant characteristic of the TDK 5KW is its modular design, which allows for easy integration into existing systems. The power supply features a compact footprint, making it ideal for installations where space is at a premium. Moreover, its robust construction ensures that it can withstand harsh operating conditions, including extreme temperatures and vibrations.

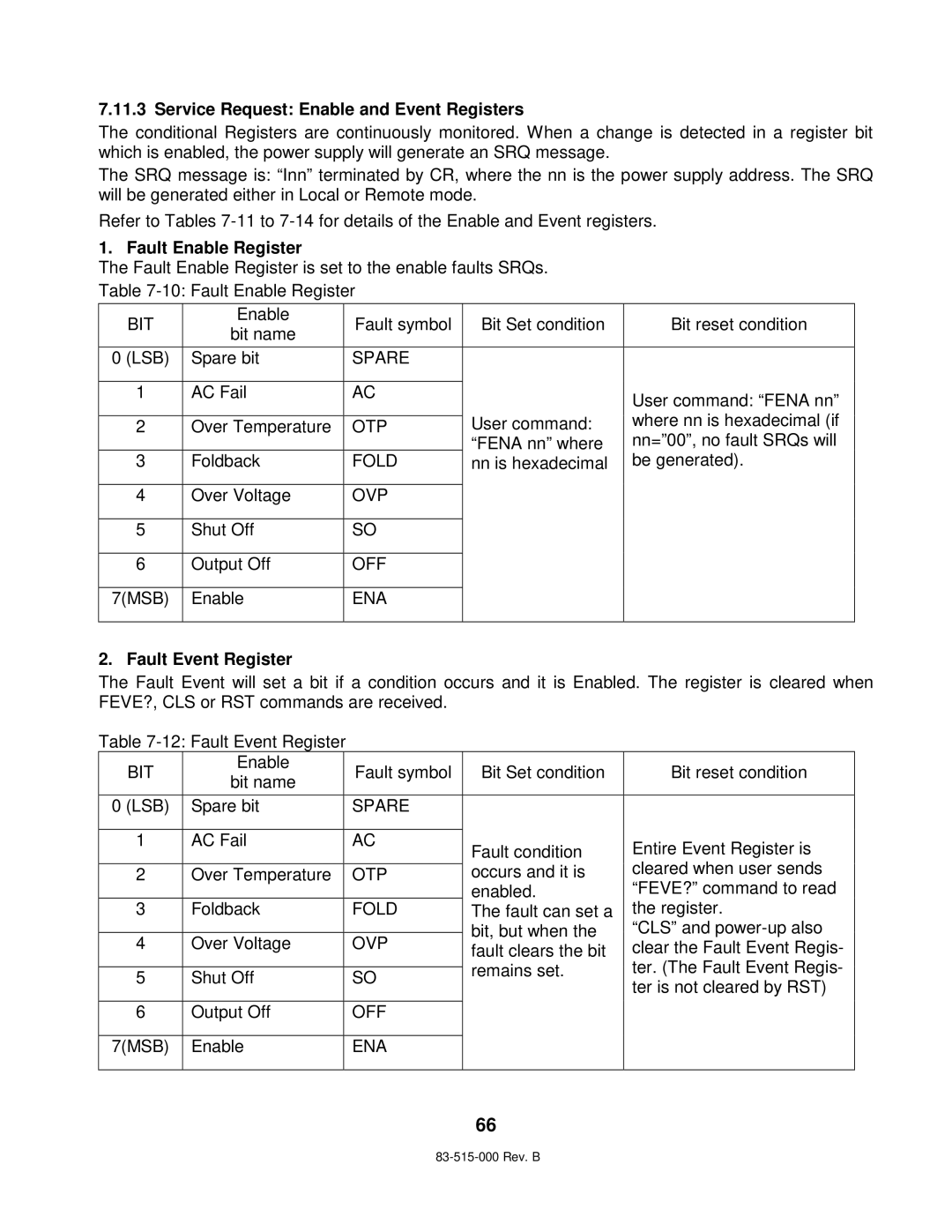

Reliability is further enhanced through built-in protection features, including overvoltage, overcurrent, and short-circuit protection. These safety mechanisms not only safeguard the power supply itself but also protect the connected equipment from damage, making it a trustworthy choice for critical applications.

The TDK 5KW also supports various communication protocols, enabling seamless integration into modern automation systems. This feature allows for real-time monitoring and control, providing users with essential data to optimize performance and troubleshoot issues efficiently.

In summary, the TDK 5KW is a powerful, efficient, and reliable power supply solution that caters to a broad range of applications. Its advanced technologies, modular design, and robust safety features make it an essential component for anyone looking to enhance their electrical systems with a high-quality power source.