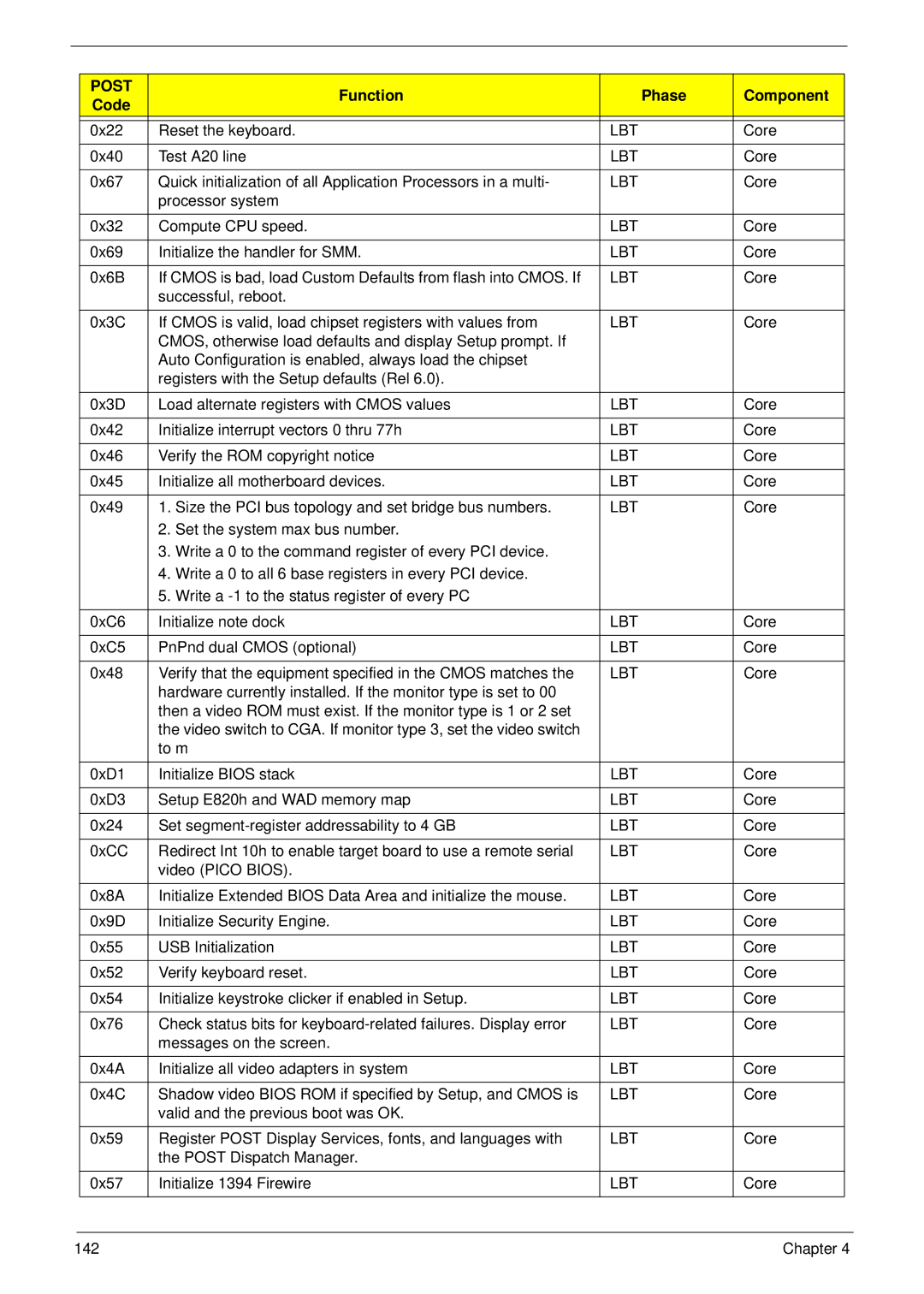

POST | Function | Phase | Component | |

Code | ||||

|

|

| ||

|

|

|

| |

0x22 | Reset the keyboard. | LBT | Core | |

|

|

|

| |

0x40 | Test A20 line | LBT | Core | |

|

|

|

| |

0x67 | Quick initialization of all Application Processors in a multi- | LBT | Core | |

| processor system |

|

| |

|

|

|

| |

0x32 | Compute CPU speed. | LBT | Core | |

|

|

|

| |

0x69 | Initialize the handler for SMM. | LBT | Core | |

|

|

|

| |

0x6B | If CMOS is bad, load Custom Defaults from flash into CMOS. If | LBT | Core | |

| successful, reboot. |

|

| |

|

|

|

| |

0x3C | If CMOS is valid, load chipset registers with values from | LBT | Core | |

| CMOS, otherwise load defaults and display Setup prompt. If |

|

| |

| Auto Configuration is enabled, always load the chipset |

|

| |

| registers with the Setup defaults (Rel 6.0). |

|

| |

|

|

|

| |

0x3D | Load alternate registers with CMOS values | LBT | Core | |

|

|

|

| |

0x42 | Initialize interrupt vectors 0 thru 77h | LBT | Core | |

|

|

|

| |

0x46 | Verify the ROM copyright notice | LBT | Core | |

|

|

|

| |

0x45 | Initialize all motherboard devices. | LBT | Core | |

|

|

|

| |

0x49 | 1. Size the PCI bus topology and set bridge bus numbers. | LBT | Core |

2.Set the system max bus number.

3.Write a 0 to the command register of every PCI device.

4.Write a 0 to all 6 base registers in every PCI device.

5.Write a

0xC6 | Initialize note dock | LBT | Core |

0xC5 | PnPnd dual CMOS (optional) | LBT | Core |

|

|

|

|

0x48 | Verify that the equipment specified in the CMOS matches the | LBT | Core |

| hardware currently installed. If the monitor type is set to 00 |

|

|

| then a video ROM must exist. If the monitor type is 1 or 2 set |

|

|

| the video switch to CGA. If monitor type 3, set the video switch |

|

|

| to m |

|

|

|

|

|

|

0xD1 | Initialize BIOS stack | LBT | Core |

|

|

|

|

0xD3 | Setup E820h and WAD memory map | LBT | Core |

|

|

|

|

0x24 | Set | LBT | Core |

|

|

|

|

0xCC | Redirect Int 10h to enable target board to use a remote serial | LBT | Core |

| video (PICO BIOS). |

|

|

|

|

|

|

0x8A | Initialize Extended BIOS Data Area and initialize the mouse. | LBT | Core |

|

|

|

|

0x9D | Initialize Security Engine. | LBT | Core |

|

|

|

|

0x55 | USB Initialization | LBT | Core |

|

|

|

|

0x52 | Verify keyboard reset. | LBT | Core |

|

|

|

|

0x54 | Initialize keystroke clicker if enabled in Setup. | LBT | Core |

|

|

|

|

0x76 | Check status bits for | LBT | Core |

| messages on the screen. |

|

|

|

|

|

|

0x4A | Initialize all video adapters in system | LBT | Core |

|

|

|

|

0x4C | Shadow video BIOS ROM if specified by Setup, and CMOS is | LBT | Core |

| valid and the previous boot was OK. |

|

|

|

|

|

|

0x59 | Register POST Display Services, fonts, and languages with | LBT | Core |

| the POST Dispatch Manager. |

|

|

|

|

|

|

0x57 | Initialize 1394 Firewire | LBT | Core |

142 | Chapter 4 |