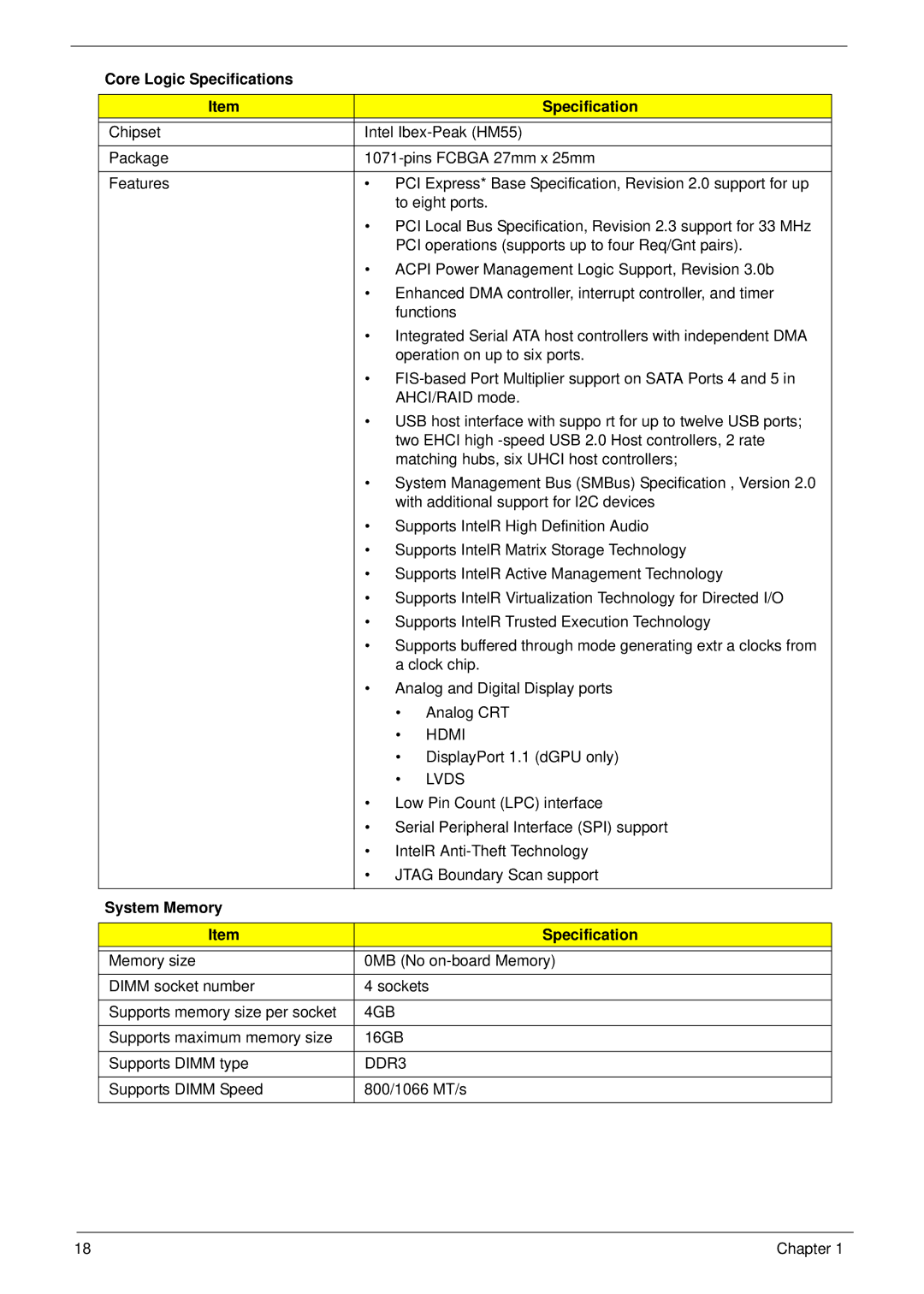

Core Logic Specifications

Item |

| Specification |

|

| |

Chipset | Intel | |

Package | ||

|

| |

Features | • PCI Express* Base Specification, Revision 2.0 support for up | |

| to eight ports. | |

| • PCI Local Bus Specification, Revision 2.3 support for 33 MHz | |

| PCI operations (supports up to four Req/Gnt pairs). | |

| • ACPI Power Management Logic Support, Revision 3.0b | |

| • Enhanced DMA controller, interrupt controller, and timer | |

| functions | |

| • Integrated Serial ATA host controllers with independent DMA | |

| operation on up to six ports. | |

| • | |

| AHCI/RAID mode. | |

| • USB host interface with suppo rt for up to twelve USB ports; | |

| two EHCI high | |

| matching hubs, six UHCI host controllers; | |

| • System Management Bus (SMBus) Specification , Version 2.0 | |

| with additional support for I2C devices | |

| • Supports IntelR High Definition Audio | |

| • Supports IntelR Matrix Storage Technology | |

| • Supports IntelR Active Management Technology | |

| • Supports IntelR Virtualization Technology for Directed I/O | |

| • Supports IntelR Trusted Execution Technology | |

| • Supports buffered through mode generating extr a clocks from | |

| a clock chip. | |

| • Analog and Digital Display ports | |

| • | Analog CRT |

| • | HDMI |

| • DisplayPort 1.1 (dGPU only) | |

| • | LVDS |

| • Low Pin Count (LPC) interface | |

| • Serial Peripheral Interface (SPI) support | |

| • IntelR | |

| • JTAG Boundary Scan support | |

|

|

|

System Memory |

|

|

|

|

|

Item |

| Specification |

|

| |

Memory size | 0MB (No | |

|

| |

DIMM socket number | 4 sockets | |

|

|

|

Supports memory size per socket | 4GB |

|

|

|

|

Supports maximum memory size | 16GB |

|

|

|

|

Supports DIMM type | DDR3 |

|

|

| |

Supports DIMM Speed | 800/1066 MT/s | |

|

|

|

18 | Chapter 1 |