Versatile Interface Processor Functions

Note The VIP port adapters themselves do not support OIR, nor are they FRUs.

The VIP uses a Reduced Instructions Set Computing (RISC), Mips 4600 processor for high performance, and has an internal operating frequency of 100 megahertz (MHz) and a

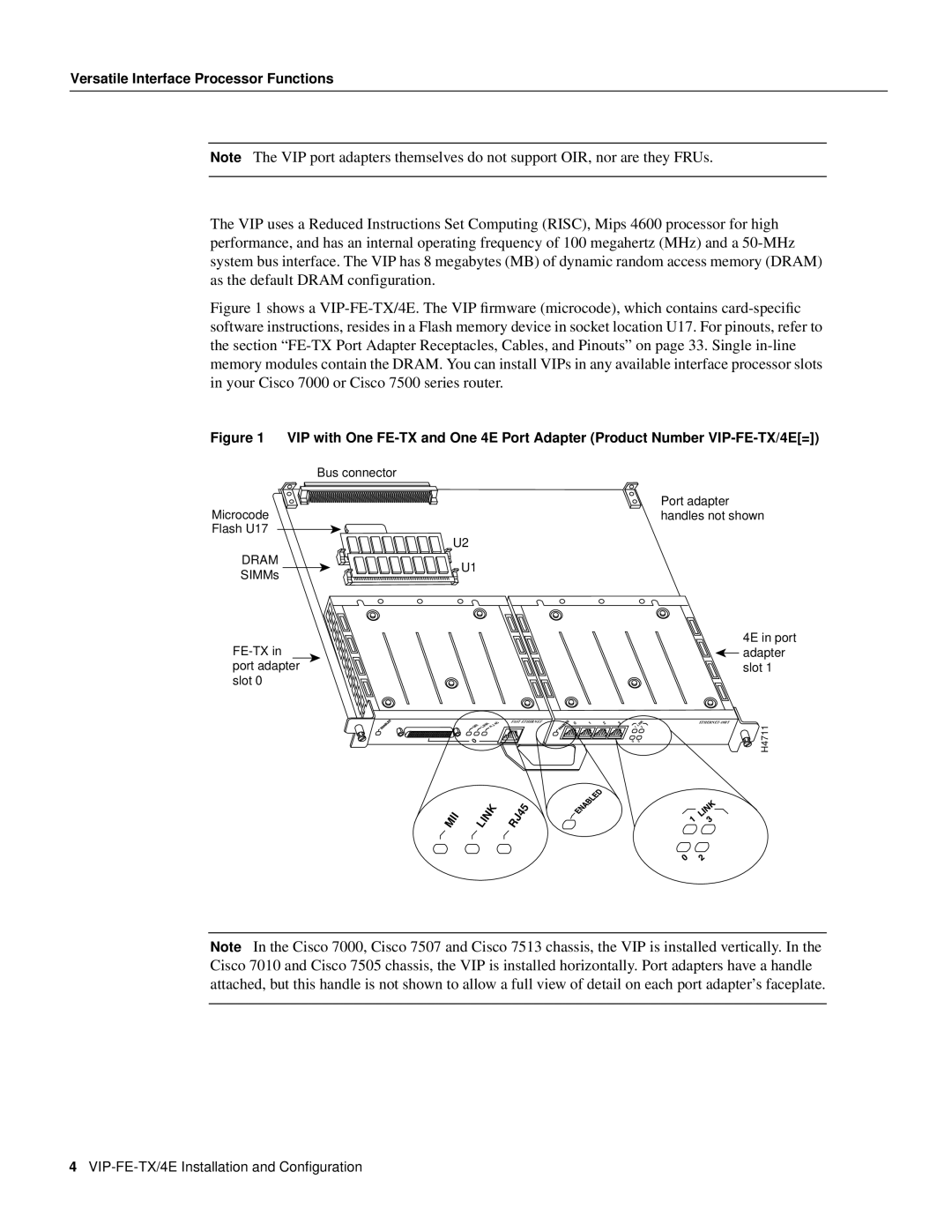

Figure 1 shows a VIP-FE-TX/4E. The VIP firmware (microcode), which contains card-specific software instructions, resides in a Flash memory device in socket location U17. For pinouts, refer to the section “FE-TX Port Adapter Receptacles, Cables, and Pinouts” on page 33. Single in-line memory modules contain the DRAM. You can install VIPs in any available interface processor slots in your Cisco 7000 or Cisco 7500 series router.

Figure 1 VIP with One FE-TX and One 4E Port Adapter (Product Number VIP-FE-TX/4E[=])

| Bus connector | |

Microcode | Port adapter | |

handles not shown | ||

Flash U17 | U2 | |

| ||

DRAM | U1 | |

SIMMs | ||

| ||

4E in port | ||

adapter | ||

port adapter | slot 1 | |

slot 0 |

|

FAST ETHERNET

0

MII | LINK | RJ45 |

0 | 1 | 2 | 3 |

1 | LINK |

3 | |

0 | 2 |

H4711

Note In the Cisco 7000, Cisco 7507 and Cisco 7513 chassis, the VIP is installed vertically. In the Cisco 7010 and Cisco 7505 chassis, the VIP is installed horizontally. Port adapters have a handle attached, but this handle is not shown to allow a full view of detail on each port adapter’s faceplate.

4