CY24272

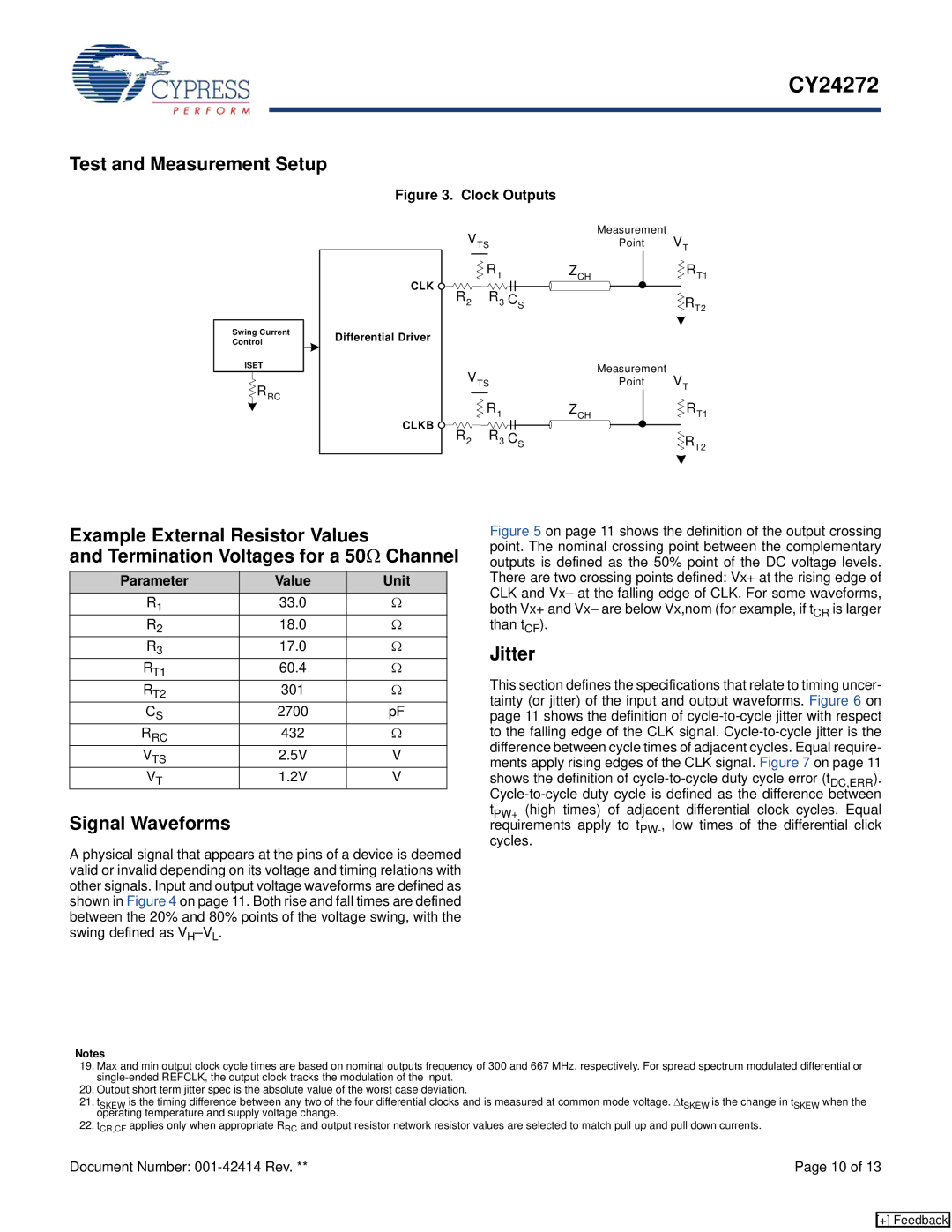

Test and Measurement Setup

Swing Current Control

ISET

![]() RRC

RRC

Figure 3. Clock Outputs

| VTS |

| Measurement |

| |

|

| Point V | T | ||

|

|

|

|

| |

CLK |

| R1 | ZCH |

| RT1 |

R2 | R3 CS |

|

| RT2 | |

|

|

| |||

Differential Driver

| VTS |

| Measurement | V |

|

| |

|

| Point | T |

| |||

|

|

|

|

|

|

| |

CLKB |

| R1 | ZCH |

|

| RT1 | |

R2 | R3 CS |

|

|

| R |

| |

|

|

|

| T2 | |||

|

|

|

|

|

|

| |

Example External Resistor Values

and Termination Voltages for a 50Ω Channel

Parameter | Value | Unit |

R1 | 33.0 | Ω |

R2 | 18.0 | Ω |

R3 | 17.0 | Ω |

RT1 | 60.4 | Ω |

RT2 | 301 | Ω |

CS | 2700 | pF |

RRC | 432 | Ω |

VTS | 2.5V | V |

VT | 1.2V | V |

Signal Waveforms

A physical signal that appears at the pins of a device is deemed valid or invalid depending on its voltage and timing relations with other signals. Input and output voltage waveforms are defined as shown in Figure 4 on page 11. Both rise and fall times are defined between the 20% and 80% points of the voltage swing, with the swing defined as

Figure 5 on page 11 shows the definition of the output crossing point. The nominal crossing point between the complementary outputs is defined as the 50% point of the DC voltage levels. There are two crossing points defined: Vx+ at the rising edge of CLK and Vx– at the falling edge of CLK. For some waveforms, both Vx+ and Vx– are below Vx,nom (for example, if tCR is larger than tCF).

Jitter

This section defines the specifications that relate to timing uncer- tainty (or jitter) of the input and output waveforms. Figure 6 on page 11 shows the definition of

Notes

19.Max and min output clock cycle times are based on nominal outputs frequency of 300 and 667 MHz, respectively. For spread spectrum modulated differential or

20.Output short term jitter spec is the absolute value of the worst case deviation.

21.tSKEW is the timing difference between any two of the four differential clocks and is measured at common mode voltage. ΔtSKEW is the change in tSKEW when the operating temperature and supply voltage change.

22.tCR,CF applies only when appropriate RRC and output resistor network resistor values are selected to match pull up and pull down currents.

Document Number: | Page 10 of 13 |

[+] Feedback