|

|

|

|

|

| CY24272 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

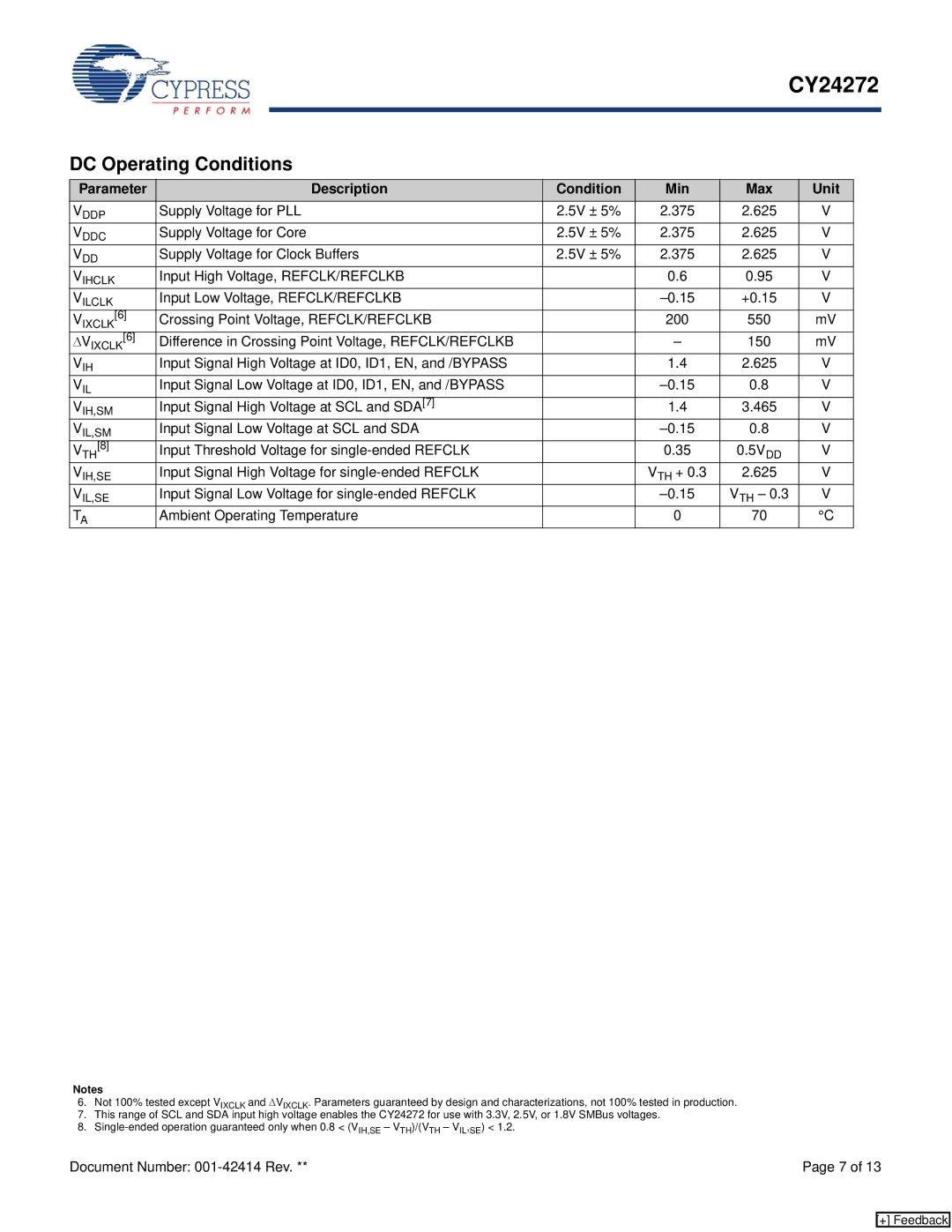

DC Operating Conditions |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| |

Parameter |

|

| Description | Condition | Min | Max | Unit |

|

|

VDDP | Supply Voltage for PLL | 2.5V ± 5% | 2.375 | 2.625 | V |

|

| ||

VDDC | Supply Voltage for Core | 2.5V ± 5% | 2.375 | 2.625 | V |

|

| ||

VDD | Supply Voltage for Clock Buffers | 2.5V ± 5% | 2.375 | 2.625 | V |

|

| ||

VIHCLK | Input High Voltage, REFCLK/REFCLKB |

| 0.6 | 0.95 | V |

|

| ||

VILCLK | Input Low Voltage, REFCLK/REFCLKB |

| +0.15 | V |

|

| |||

VIXCLK[6] | Crossing Point Voltage, REFCLK/REFCLKB |

| 200 | 550 | mV |

|

| ||

ΔVIXCLK[6] | Difference in Crossing Point Voltage, REFCLK/REFCLKB |

| – | 150 | mV |

|

| ||

VIH | Input Signal High Voltage at ID0, ID1, EN, and /BYPASS |

| 1.4 | 2.625 | V |

|

| ||

VIL | Input Signal Low Voltage at ID0, ID1, EN, and /BYPASS |

| 0.8 | V |

|

| |||

VIH,SM | Input Signal High Voltage at SCL and SDA[7] |

| 1.4 | 3.465 | V |

|

| ||

VIL,SM | Input Signal Low Voltage at SCL and SDA |

| 0.8 | V |

|

| |||

VTH[8] | Input Threshold Voltage for |

| 0.35 | 0.5VDD | V |

|

| ||

VIH,SE | Input Signal High Voltage for |

| VTH + 0.3 | 2.625 | V |

|

| ||

VIL,SE | Input Signal Low Voltage for |

| VTH – 0.3 | V |

|

| |||

TA | Ambient Operating Temperature |

| 0 | 70 | °C |

|

| ||

Notes

6.Not 100% tested except VIXCLK and ΔVIXCLK. Parameters guaranteed by design and characterizations, not 100% tested in production.

7.This range of SCL and SDA input high voltage enables the CY24272 for use with 3.3V, 2.5V, or 1.8V SMBus voltages.

8.

Document Number: | Page 7 of 13 |

[+] Feedback