CY7C1316JV18, CY7C1916JV18 CY7C1318JV18, CY7C1320JV18

18-Mbit DDR-II SRAM 2-Word Burst Architecture

Features

■

■300 MHz clock for high bandwidth

■

■Double Data Rate (DDR) interfaces

(data transferred at 600 MHz) at 300 MHz

■Two input clocks (K and K) for precise DDR timing ❐ SRAM uses rising edges only

■Two input clocks for output data (C and C) to minimize clock skew and flight time mismatches

■Echo clocks (CQ and CQ) simplify data capture in

■Synchronous internally

■

■Operates similar to a

■1.8V core power supply with HSTL inputs and outputs

■Variable drive HSTL output buffers

■Expanded HSTL output voltage

■Available in

■Offered in both

■JTAG 1149.1 compatible test access port

■Delay Lock Loop (DLL) for accurate data placement

Functional Description

The CY7C1316JV18, CY7C1916JV18, CY7C1318JV18, and CY7C1320JV18 are 1.8V Synchronous Pipelined SRAMs equipped with

Asynchronous inputs include an output impedance matching input (ZQ). Synchronous data outputs (Q, sharing the same physical pins as the data inputs, D) are tightly matched to the two output echo clocks CQ/CQ, eliminating the need to capture data separately from each individual DDR SRAM in the system design. Output data clocks (C/C) enable maximum system clocking and data synchronization flexibility.

All synchronous inputs pass through input registers controlled by the K or K input clocks. All data outputs pass through output registers controlled by the C or C (or K or K in a single clock domain) input clocks. Writes are conducted with

Configurations

CY7C1316JV18 – 2M x 8

CY7C1916JV18 – 2M x 9

CY7C1318JV18 – 1M x 18

CY7C1320JV18 – 512K x 36

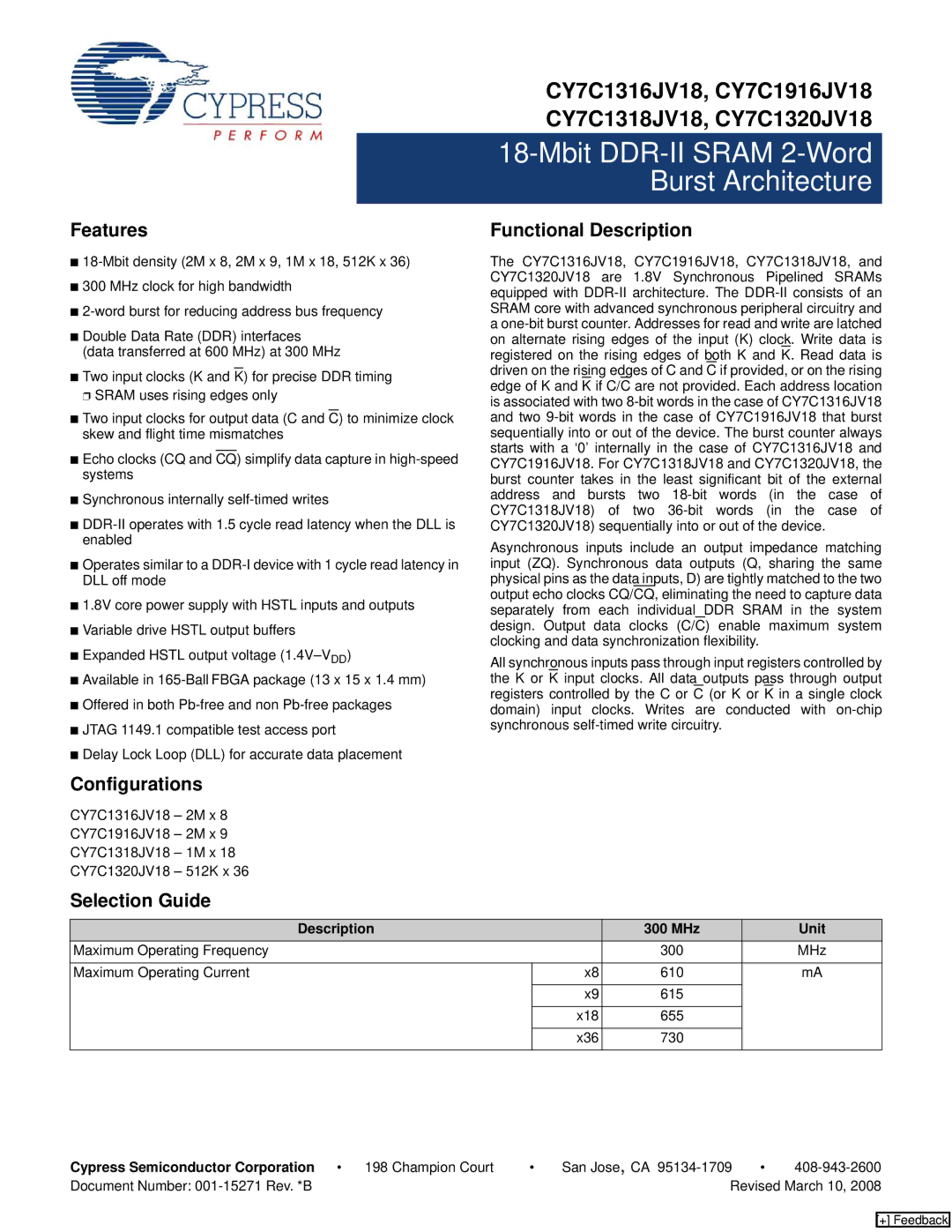

Selection Guide

| Description | 300 MHz | Unit | |

Maximum Operating Frequency |

|

| 300 | MHz |

|

|

|

|

|

Maximum Operating Current |

| x8 | 610 | mA |

|

|

|

|

|

|

| x9 | 615 |

|

|

|

|

|

|

|

| x18 | 655 |

|

|

|

|

|

|

|

| x36 | 730 |

|

|

|

|

|

|

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised March 10, 2008 | ||

[+] Feedback