|

|

|

|

|

|

|

|

|

|

|

|

|

| CY7C1330AV25 | |

|

|

|

|

|

|

|

|

|

|

|

| PRELIMINARY | CY7C1332AV25 | ||

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

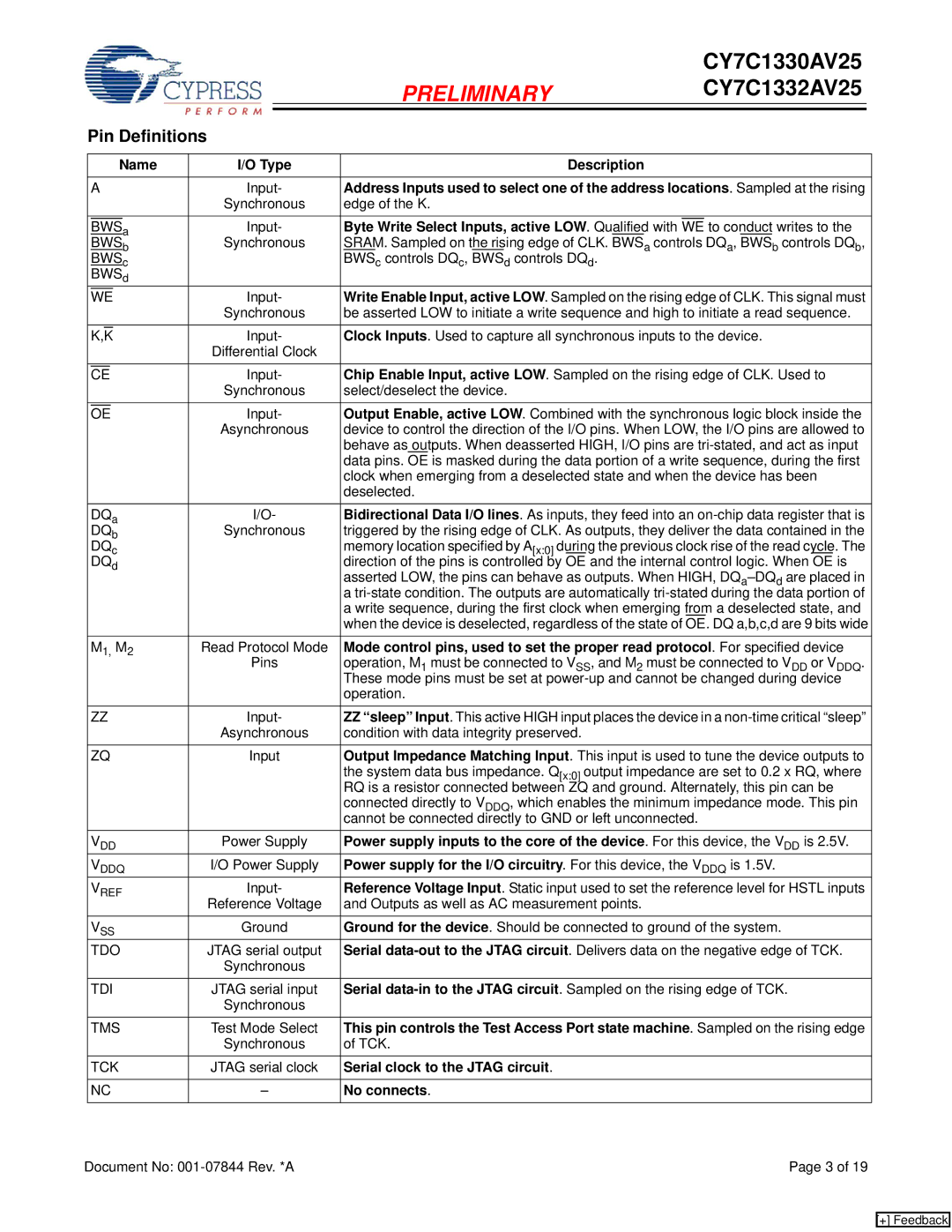

| Pin Definitions |

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

| Name | I/O Type | Description |

|

| ||||

|

|

|

|

| |||||||||||

|

| A | Input- | Address Inputs used to select one of the address locations. Sampled at the rising | |||||||||||

|

|

|

|

|

|

|

|

| Synchronous | edge of the K. |

|

| |||

|

|

|

|

|

|

|

| a | Input- | Byte Write Select Inputs, active LOW. Qualified with |

| to conduct writes to the | |||

|

| BWS | WE | ||||||||||||

|

| BWSb | Synchronous | SRAM. Sampled on the rising edge of CLK. BWSa controls DQa, BWSb controls DQb, | |||||||||||

|

| BWSc |

|

|

| BWSc controls DQc, BWSd controls DQd. |

|

| |||||||

|

| BWSd |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| Input- | Write Enable Input, active LOW. Sampled on the rising edge of CLK. This signal must | ||||||

|

| WE | |||||||||||||

|

|

|

|

|

|

|

|

| Synchronous | be asserted LOW to initiate a write sequence and high to initiate a read sequence. | |||||

|

|

|

|

|

|

|

|

| Input- | Clock Inputs. Used to capture all synchronous inputs to the device. | |||||

|

| K,K |

| ||||||||||||

|

|

|

|

|

|

|

|

| Differential Clock |

|

|

|

| ||

|

|

|

|

|

| Input- | Chip Enable Input, active LOW. Sampled on the rising edge of CLK. Used to | ||||||||

|

| CE | |||||||||||||

|

|

|

|

|

|

|

|

| Synchronous | select/deselect the device. |

|

| |||

|

|

|

|

|

| Input- | Output Enable, active LOW. Combined with the synchronous logic block inside the | ||||||||

|

| OE | |||||||||||||

|

|

|

|

|

|

|

|

| Asynchronous | device to control the direction of the I/O pins. When LOW, the I/O pins are allowed to | |||||

|

|

|

|

|

|

|

|

|

|

|

| behave as outputs. When deasserted HIGH, I/O pins are | |||

|

|

|

|

|

|

|

|

|

|

|

| data pins. OE is masked during the data portion of a write sequence, during the first | |||

|

|

|

|

|

|

|

|

|

|

|

| clock when emerging from a deselected state and when the device has been | |||

|

|

|

|

|

|

|

|

|

|

|

| deselected. |

|

| |

|

| DQa | I/O- | Bidirectional Data I/O lines. As inputs, they feed into an | |||||||||||

|

| DQb | Synchronous | triggered by the rising edge of CLK. As outputs, they deliver the data contained in the | |||||||||||

|

| DQc |

|

|

| memory location specified by A[x:0] during the previous clock rise of the read cycle. The | |||||||||

|

| DQd |

|

|

| direction of the pins is controlled by OE and the internal control logic. When OE is | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| asserted LOW, the pins can behave as outputs. When HIGH, | |||

|

|

|

|

|

|

|

|

|

|

|

| a | |||

|

|

|

|

|

|

|

|

|

|

|

| a write sequence, during the first clock when emerging from a deselected state, and | |||

|

|

|

|

|

|

|

|

|

|

|

| when the device is deselected, regardless of the state of OE. DQ a,b,c,d are 9 bits wide | |||

|

| M1, M2 | Read Protocol Mode | Mode control pins, used to set the proper read protocol. For specified device | |||||||||||

|

|

|

|

|

|

|

|

| Pins | operation, M1 must be connected to VSS, and M2 must be connected to VDD or VDDQ. | |||||

|

|

|

|

|

|

|

|

|

|

|

| These mode pins must be set at | |||

|

|

|

|

|

|

|

|

|

|

|

| operation. |

|

| |

|

| ZZ | Input- | ZZ “sleep” Input. This active HIGH input places the device in a | |||||||||||

|

|

|

|

|

|

|

|

| Asynchronous | condition with data integrity preserved. |

|

| |||

|

| ZQ | Input | Output Impedance Matching Input. This input is used to tune the device outputs to | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

| the system data bus impedance. Q[x:0] output impedance are set to 0.2 x RQ, where | |||

|

|

|

|

|

|

|

|

|

|

|

| RQ is a resistor connected between ZQ and ground. Alternately, this pin can be | |||

|

|

|

|

|

|

|

|

|

|

|

| connected directly to VDDQ, which enables the minimum impedance mode. This pin | |||

|

|

|

|

|

|

|

|

|

|

|

| cannot be connected directly to GND or left unconnected. |

|

| |

|

| VDD | Power Supply | Power supply inputs to the core of the device. For this device, the VDD is 2.5V. | |||||||||||

|

| VDDQ | I/O Power Supply | Power supply for the I/O circuitry. For this device, the VDDQ is 1.5V. | |||||||||||

|

| VREF | Input- | Reference Voltage Input. Static input used to set the reference level for HSTL inputs | |||||||||||

|

|

|

|

|

|

|

|

| Reference Voltage | and Outputs as well as AC measurement points. |

|

| |||

|

| VSS | Ground | Ground for the device. Should be connected to ground of the system. | |||||||||||

|

| TDO | JTAG serial output | Serial | |||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

|

|

|

| ||

|

| TDI | JTAG serial input | Serial | |||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

|

|

|

| ||

|

| TMS | Test Mode Select | This pin controls the Test Access Port state machine. Sampled on the rising edge | |||||||||||

|

|

|

|

|

|

|

|

| Synchronous | of TCK. |

|

| |||

|

| TCK | JTAG serial clock | Serial clock to the JTAG circuit. |

|

| |||||||||

|

|

|

|

|

|

| |||||||||

|

| NC | – | No connects. |

|

| |||||||||

|

|

|

|

|

| ||||||||||

Document No: |

|

| Page 3 of 19 | ||||||||||||

[+] Feedback