Main

Document Revision History

Please see http://www.freescale.com for the most current Data Sheet revision.

56F8322/56F8122 Block Diagram

56F8322 Technical Data, Rev. 10.0 Freescale Semiconductor 3

16-Bit 56800E Core

56F8322/56F8122 General Description

Note: Features in italics are NOT available in the 56F8122 device.

Table of Contents

Part 1: Overview . . . . . . . . . . . . . . . . . . . . . . 5

Part 2: Signal/Connection Descriptions . . 14

Part 13: Ordering Information . . . . . . . . . 135

Part 3: On-Chip Clock Synthesis (OCCS) . 26

Part 1 Overview

1.1 56F8322/56F8122 Features

1.1.1 Hybrid Controller Core

1.1.2 Differences Between Devices

1.1.3 Memory

Note: Features in italics are NOT available in the 56F8122 device.

1.1.4 Peripheral Circuits

Note: Features in italics are NOT available in the 56F8122 device.

1.1.5 Energy Information

1.2 Device Description

1.2.1 56F8322 Features

1.2.2 56F8122 Features

1.3 Award-Winning Development Environment

1.4 Architecture Block Diagram

Figure 1-1 System Bus Interfaces

56800E

Figure 1-2 Peripheral Subsystem

To/From IPBus Bridge

Table 1-2 Bus Signal Names

1.5 Product Documentation

Table 1-3

This data sheet uses the following conventions:

The documents listed in

. Table 1-3 Chip Documentation

Part 2 Signal/Connection Descriptions

2.1 Introduction

Table2-1 Functional Group Pin Allocations

56F8322

Figure 2-1 56F8322 Signals Identified by Functional Group (48-Pin LQFP)

Note: VREFH is tied to VDDA and VREFLO is tied to VSSA inside this package

56F8322 Technical Data, Rev. 10.0 Freescale Semiconductor 15

56F8122

Figure 2-2 56F8122 Signals Identified by Functional Group (48-Pin LQFP)

56F8322 Techncial Data, Rev. 10.0 16 Freescale Semiconductor

2.2 Signal Pins

Page

Page

Page

Page

Page

Page

Page

Page

Part 3 On-Chip Clock Synthesis (OCCS)

3.1 Introduction

3.2 External Clock Operation

3.2.1 Crystal Oscillator

3.2.2 Ceramic Resonator (Default)

3.2.3 External Clock Source

3.3 Use of On-Chip Relaxation Oscillator

3.4 Internal Clock Operation

Figure 3-4 Internal Clock Operation

3.5 Registers

Part 4 Memory Map

4.1 Introduction

4.2 Program Map

4.3 Interrupt Vector Table

Page

Table 4-3 Interrupt Vector Table Contents1 (Continued)

4.4 Data Map

4.5 Flash Memory Map

Page

4.6 EOnCE Memory Map

4.7 Peripheral Memory Mapped Registers

Table 4-6 EOnCE Memory Map

Table 4-8 Quad Timer A Registers Address Map (TMRA_BASE = $00 F040)

Table 4-8 Quad Timer A Registers Address Map (Continued) (TMRA_BASE = $00 F040)

Table 4-9 Quad Timer C Registers Address Map (TMRC_BASE = $00 F0C0)

Table 4-9 Quad Timer C Registers Address Map (Continued) (TMRC_BASE = $00 F0C0)

Table 4-12 Interrupt Control Registers Address Map

Table 4-13 Analog to Digital Converter Registers Address Map (ADCA_BASE = $00 F200)

Table 4-12 Interrupt Control Registers Address Map (Continued)

Page

Page

Table 4-20 Clock Generation Module Registers Address Map (CLKGEN_BASE = $00 F2D0)

Table 4-21 GPIOA Registers Address Map (GPIOA_BASE = $00 F2E0)

Table 4-22 GPIOB Registers Address Map (GPIOB_BASE = $00 F300)

Table 4-23 GPIOC Registers Address Map (GPIOC_BASE = $00F310)

Table 4-24 System Integration Module Registers Address Map (SIM_BASE = $00 F350)

Table 4-25 Power Supervisor Registers Address Map (LVI_BASE = $00 F360)

Table 4-26 Flash Module Registers Address Map (FM_BASE = $00 F400)

Table 4-27 FlexCAN Registers Address Map

Page

Page

Page

Page

4.8 Factory-Programmed Memory

Part 5 Interrupt Controller (ITCN)

5.1 Introduction

5.2 Features

5.3 Functional Description

5.3.1 Normal Interrupt Handling

5.3.2 Interrupt Nesting

5.3.3 Fast Interrupt Handling

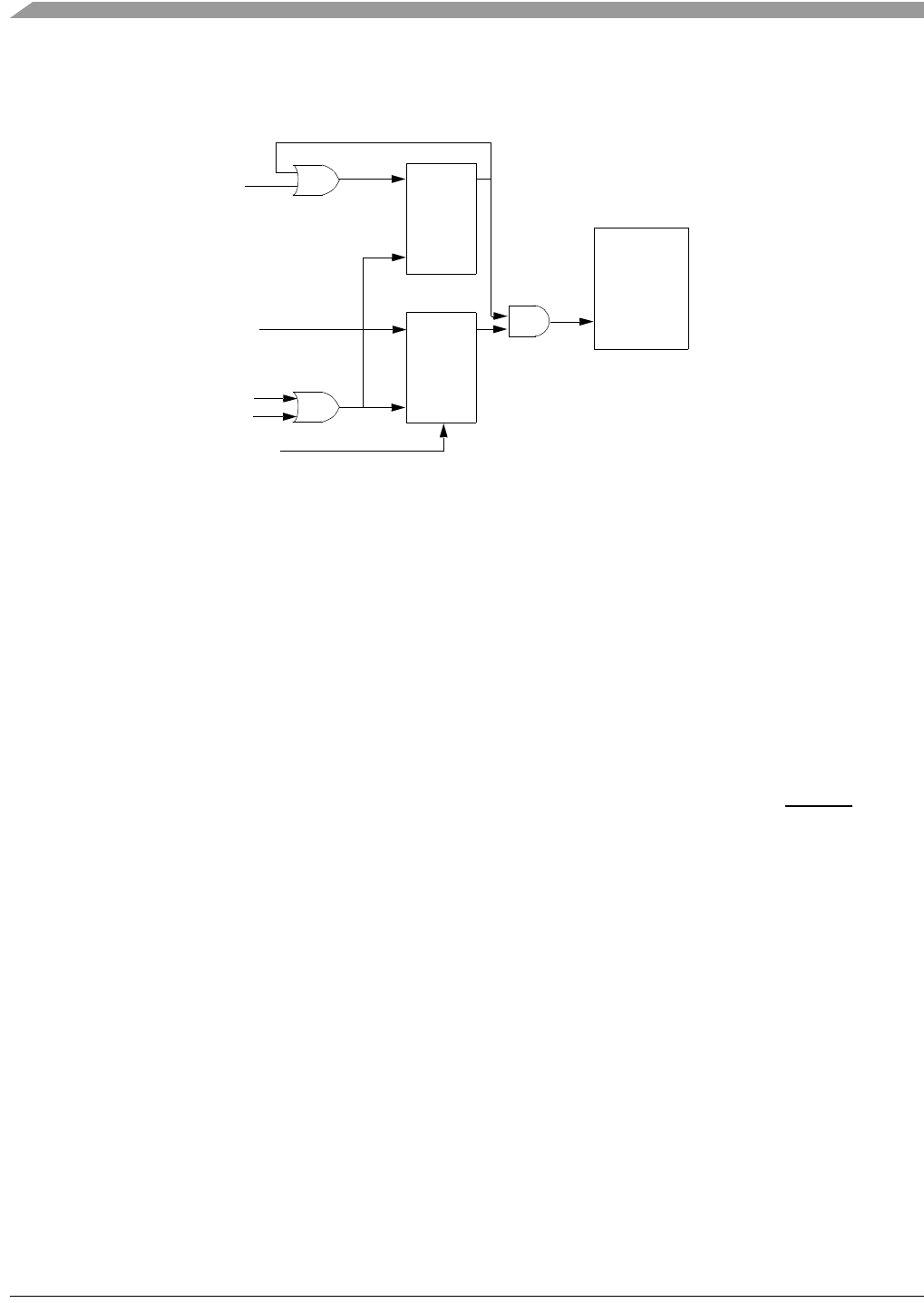

5.4 Block Diagram

Figure 5-1 Interrupt Controller Block Diagram

5.5 Operating Modes

The ITCN module design contains two major modes of operation:

5.6 Register Descriptions

Figure 5-2 ITCN Register Map Summary

56F8322 Techncial Data, Rev. 10.0 56 Freescale Semiconductor

5.6.1 Interrupt Priority Register 0 (IPR0)

5.6.1.1 ReservedBits 1514

5.6.1.2 EOnCE Breakpoint Unit 0 Interrupt Priority Level (BKPT_U0 IPL) Bits1312

5.6.1.3 EOnCE Step Counter Interrupt Priority Level (STPCNT IPL)

5.6.1.4 ReservedBits 90

5.6.3 Interrupt Priority Register 2 (IPR2)

Page

5.6.3.5 Low Voltage Detector Interrupt Priority Level (LVI IPL)Bits 76

5.6.3.6 ReservedBits 52

5.6.3.7 External IRQ A Interrupt Priority Level (IRQA IPL)Bits 10

5.6.4 Interrupt Priority Register 3 (IPR3)

5.6.4.1 ReservedBits 1510

5.6.4.2 FlexCAN Message Buffer Interrupt Priority Level (FCMSGBUF IPL)Bits 98

5.6.4.3 FlexCAN Wake Up Interrupt Priority Level (FCWKUP IPL) Bits 76

5.6.4.4 FlexCAN Error Interrupt Priority Level (FCERR IPL) Bits 54

5.6.5 Interrupt Priority Register 4 (IPR4)

Page

5.6.5.6 GPIO_B Interrupt Priority Level (GPIOB IPL)Bits 32

5.6.5.7 GPIO_C Interrupt Priority Level (GPIOC IPL)Bits 10

5.6.6 Interrupt Priority Register 5 (IPR5)

Figure 5-8 Interrupt Priority Register 5 (IPR5)

5.6.6.1 ReservedBits 1512

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

5.6.6.2 SCI1 Receiver Full Interrupt Priority Level (SCI1_RCV IPL) Bits 1110

Page

5.6.7 Interrupt Priority Register 6 (IPR6)

5.6.7.1 Timer C, Channel 0 Interrupt Priority Level (TMRC_0 IPL) Bits 1514

5.6.7.2 ReservedBits 134

5.6.7.3 Quadrature Decoder 0, INDEX Pulse Interrupt Priority Level (DEC0_XIRQ IPL)Bits 32

5.6.8 Interrupt Priority Register 7 (IPR7)

5.6.8.1 Timer A, Channel 0 Interrupt Priority Level (TMRA0 IPL) Bits 1514

5.6.8.2 ReservedBits 136

5.6.8.3 Timer C, Channel 3 Interrupt Priority Level (TMRC3 IPL)Bits 54

5.6.8.4 Timer C, Channel 2 Interrupt Priority Level (TMRC2 IPL)Bits 32

5.6.9 Interrupt Priority Register 8 (IPR8)

5.6.9.1 SCI0 Receiver Full Interrupt Priority Level (SCI0_RCV IPL) Bits 1514

5.6.9.2 SCI0 Receiver Error Interrupt Priority Level (SCI0_RERR IPL) Bits 1312

5.6.9.3 ReservedBits 1110

Page

5.6.9.8 Timer A, Channel 1 Interrupt Priority Level (TMRA1 IPL)Bits 10

5.6.10 Interrupt Priority Register 9 (IPR9)

5.6.10.1 PWM A Fault Interrupt Priority Level (PWMAF IPL)Bits 1514

5.6.10.2 ReservedBits 1312

5.6.10.3 Reload PWM A Interrupt Priority Level (PWMA_RL IPL) Bits 1110

5.6.10.4 ReservedBits 98

5.6.11 Vector Base Address Register (VBA)

5.6.12 Fast Interrupt 0 Match Register (FIM0)

5.6.12.1 ReservedBits 157

5.6.12.2 Fast Interrupt 0 Vector Number (FAST INTERRUPT 0)Bits 60

5.6.13 Fast Interrupt 0 Vector Address Low Register (FIVAL0)

5.6.13.1 Fast Interrupt 0 Vector Address Low (FIVAL0)Bits 150

5.6.15 Fast Interrupt 1 Match Register (FIM1)

5.6.15.1 ReservedBits 157

5.6.15.2 Fast Interrupt 1 Vector Number (FAST INTERRUPT 1)Bits 60

5.6.16 Fast Interrupt 1 Vector Address Low Register (FIVAL1)

5.6.16.1 Fast Interrupt 1 Vector Address Low (FIVAL1)Bits 150

5.6.18 IRQ Pending 0 Register (IRQP0)

5.6.18.1 IRQ Pending (PENDING)Bits 162

5.6.18.2 ReservedBit 0

5.6.19 IRQ Pending 1 Register (IRQP1)

5.6.19.1 IRQ Pending (PENDING)Bits 3217

5.6.20 IRQ Pending 2 Register (IRQP2)

5.6.20.1 IRQ Pending (PENDING)Bits 4833

5.6.21 IRQ Pending 3 Register (IRQP3)

5.6.21.1 IRQ Pending (PENDING)Bits 6449

5.6.22 IRQ Pending 4 Register (IRQP4)

5.6.23 IRQ Pending 5 Register (IRQP5)

Page

5.7 Resets

5.7.1 Reset Handshake Timing

5.7.2 ITCN After Reset

Part 6 System Integration Module (SIM)

6.1 Introduction

6.2 Features

The SIM has the following features:

6.3 Operating Modes

6.4 Operating Mode Register

6.5 Register Descriptions

56F8322 Techncial Data, Rev. 10.0 80 Freescale Semiconductor

Figure 6-2 SIM Register Map Summary

6.5.1 SIM Control Register (SIM_CONTROL)

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

Figure 6-3 SIM Control Register (SIM_CONTROL)

6.5.1.1 ReservedBits 156

Base + $0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Read

6.5.2 SIM Reset Status Register (SIM_RSTSTS)

6.5.2.1 ReservedBits 156

6.5.2.2 Software Reset (SWR)Bit 5

6.5.2.3 COP Reset (COPR)Bit 4

6.5.2.4 External Reset (EXTR)Bit 3

6.5.3 SIM Software Control Registers (SIM_SCR0, SIM_SCR1, SIM_SCR2, and SIM_SCR3)

6.5.3.1 Software Control Data 1 (FIELD)Bits 150

6.5.4 Most Significant Half of JTAG ID (SIM_MSH_ID)

6.5.5 Least Significant Half of JTAG ID (SIM_LSH_ID)

6.5.6 SIM Pull-up Disable Register (SIM_PUDR)

6.5.6.1 ReservedBits 1512

6.5.6.2 RESETBit 11

6.5.7 CLKO Select Register (SIM_CLKOSR)

6.5.7.1 ReservedBits 1510

6.5.7.2 PHASEA0 (PHSA)Bit 9

6.5.7.3 PHASEB0 (PHSB)Bit 8

6.5.7.4 INDEX0 (INDEX)Bit 7

6.5.8 SIM GPIO Peripheral Select Register (SIM_GPS)

6.5.8.1 ReservedBits 158

6.5.8.2 GPIO C6 (C6)Bit 7

6.5.8.3 GPIOC5 (C5)Bit 6

6.5.8.4 GPIOB1 (B1)Bit 5

6.5.8.5 GPIOB0 (B0)Bit 4

6.5.9 Peripheral Clock Enable Register (SIM_PCE)

Page

6.5.10 I/O Short Address Location Register (SIM_ISALH and SIM_ISALL)

6.5.10.1 Input/Output Short Address Low (ISAL[23:22])Bit 10

6.5.10.2 Input/Output Short Address Low (ISAL[21:6])Bit 150

6.6 Clock Generation Overview

6.7 Power-Down Modes

6.8 Stop and Wait Mode Disable Function

6.9 Resets

Part 7 Security Features

7.1 Operation with Security Enabled

7.2 Flash Access Blocking Mechanisms

7.2.1 Forced Operating Mode Selection

7.2.2 Disabling EOnCE Access

7.2.3 Flash Lockout Recovery

7.2.4 Product Analysis

Part 8 General Purpose Input/Output (GPIO)

8.1 Introduction

8.2 Configuration

Table 8-3 GPIO External Signals Map

8.3 Memory Maps

Part 9 Joint Test Action Group (JTAG)

9.1 JTAG Information

Part 10 Specifications

10.1 General Characteristics

Table 10-1 Absolute Maximum Ratings

Table 10-2 56F8322/56F8122 ElectroStatic Discharge (ESD) Protection

Table 10-3 Thermal Characteristics

Unit Notes

Table 10-4 Recommended Operating Conditions

10.2 DC Electrical Characteristics

Table 10-5 DC Electrical Characteristics

Table 10-6 Power-On Reset Low Voltage Parameters

Table 10-7 Current Consumption per Power Supply Pin (Typical)

On-Chip Regulator Enabled (OCR_DIS = Low)

10.2.1 Voltage Regulator Specifications

Table 10-8 Current Consumption per Power Supply Pin (Typical)

On-Chip Regulator Disabled (OCR_DIS = High)

Table 10-9. Regulator Parameters

Table 10-10. PLL Parameters

10.2.2 Temperature Sense

Note: Temperature Sensor is NOT available in the 56F8122 device.

10.3 AC Electrical Characteristics

Table 10-11 Temperature Sense Parametrics

Figure 10-2 Signal States

10.4 Flash Memory Characteristics

Table 10-12 Flash Timing Paramete rs

T

10.5 External Clock Operation Timing

Figure 10-3 External Clock Timing

Table 10-13 External Clock Operation Timing Requirements

External Clock

10.6 Phase Locked Loop Timing

10.7 Oscillator Parameters

Table 10-14 PLL Timing

Table 10-15 Crystal Oscillator Parameters

Table 10-16 Relaxation Oscillator Parameters

Figure 10-4 Frequency versus Temperature

10.8 Reset, Stop, Wait, Mode Select, and Interrupt Timing

Note: All address and data buses described here are internal.

First Fetch

Figure 10-6 External Interrupt Timing (Negative Edge-Sensitive)

Figure 10-5 Asynchronous Reset Timing

Figure 10-7 External Level-Sensitive Interrupt Timing

Figure 10-8 Recovery from Stop State Using Asynchronous Interrupt Timing

10.9 Serial Peripheral Interface (SPI) Timing

Table 10-18 SPI Timing

Figure 10-9 SPI Master Timing (CPHA = 0)

Figure 10-10 SPI Master Timing (CPHA = 1)

Figure 10-11 SPI Slave Timing (CPHA = 0)

Figure 10-12 SPI Slave Timing (CPHA = 1)

10.10 Quad Timer Timing

Figure 10-13 Timer Timing

Note: The Quadrature Decoder is NOT available in the 56F8122 device.

10.11 Quadrature Decoder Timing

Table 10-19 Timer Timing

10.12 Serial Communication Interface (SCI) Timing

Figure 10-15 RXD Pulse Width Figure 10-16 TXD Pulse Width

Table 10-21 SCI Timing

10.13 Controller Area Network (CAN) Timing

Note: CAN is NOT available in the 56F8122 device.

10.14 JTAG Timing

Figure 10-17 Bus Wakeup Detection

Table 10-22 CAN Timing

Figure 10-18 Test Clock Input Timing Diagram

Figure 10-19 Test Access Port Timing Diagram

10.15 Analog-to-Digital Converter (ADC) Parameters

Table 10-24 ADC Parameters

Table 10-24 ADC Parameters (Continued)

Page

10.16 Equivalent Circuit for ADC Inputs

10.17 Power Consumption

Page

Part 11 Packaging

11.1 56F8322 Package and Pin-Out Information

PIN 1

Figure 11-1 Top View, 56F8322 48-Pin LQFP Package

Freescale 56F8322

Table 11-1 56F8322 48-Pin LQFP Package Identification by Pin Number

11.2 56F8122 Package and Pin-Out Information

PIN 1

Figure 11-2 Top View, 56F8122 48-Pin LQFP Package

ORIENTATION MARK

Freescale 56F8122

Table 11-2 56F8122 48-Pin LQFP Package Identification by Pin Number

Figure 11-3 48-Pin LQFP Mechanical Information

56F8322 Technical Data, Rev. 10.0 Freescale Semiconductor 131

Part 12 Design Considerations

12.1 Thermal Design Considerations

12.2 Electrical Design Considerations

12.3 Power Distribution and I/O Ring Implementation

Figure 12-1 Power Management

Part 13 Ordering Information

How to Reach Us: