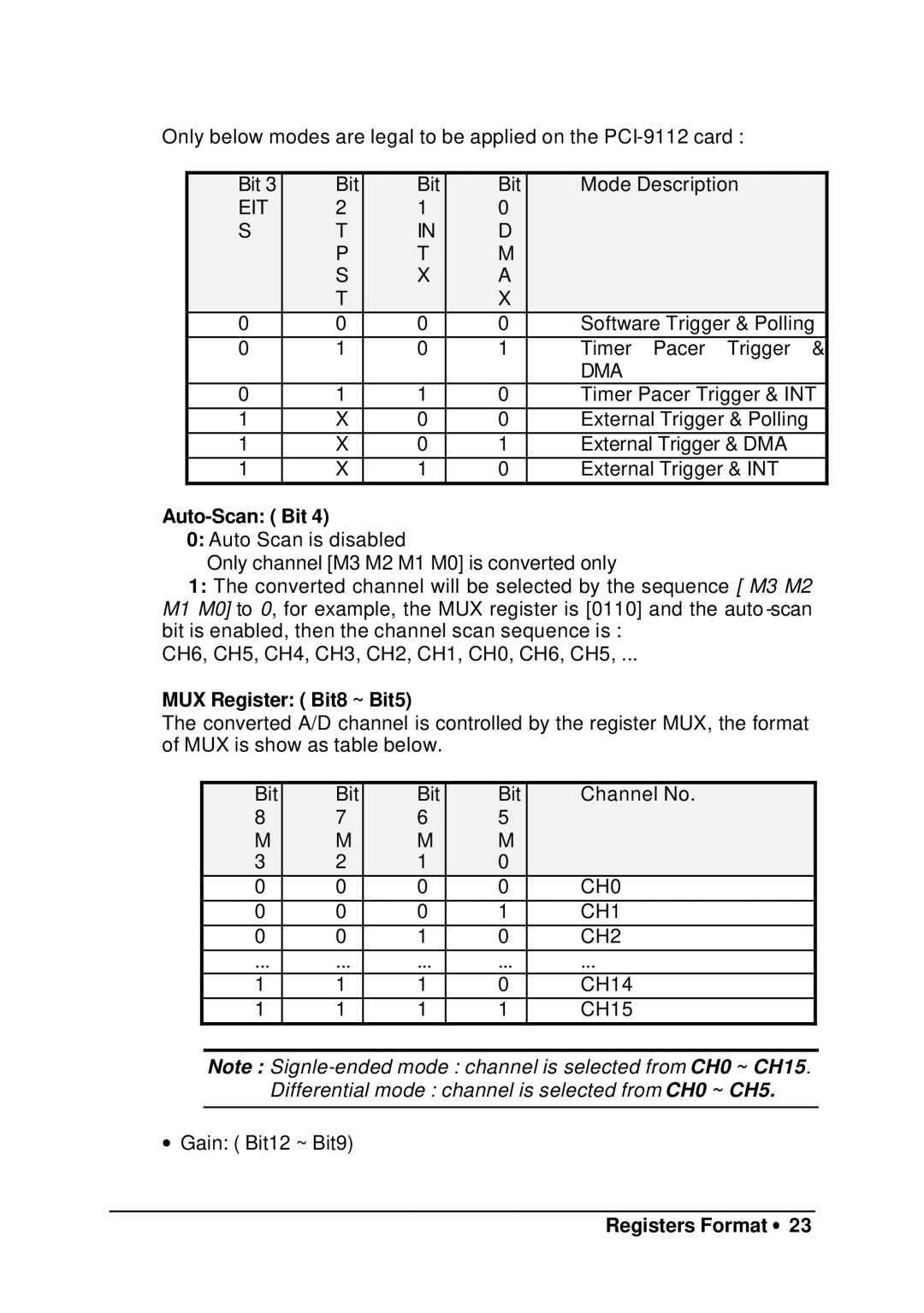

Only below modes are legal to be applied on the

Bit 3 | Bit | Bit | Bit | Mode Description |

EIT | 2 | 1 | 0 |

|

S | T | IN | D |

|

| P | T | M |

|

| S | X | A |

|

| T |

| X |

|

0 | 0 | 0 | 0 | Software Trigger & Polling |

0 | 1 | 0 | 1 | Timer Pacer Trigger & |

|

|

|

| DMA |

0 | 1 | 1 | 0 | Timer Pacer Trigger & INT |

1 | X | 0 | 0 | External Trigger & Polling |

1 | X | 0 | 1 | External Trigger & DMA |

1 | X | 1 | 0 | External Trigger & INT |

Auto-Scan: ( Bit 4)

0:Auto Scan is disabled

Only channel [M3 M2 M1 M0] is converted only

1:The converted channel will be selected by the sequence [ M3 M2 M1 M0] to 0, for example, the MUX register is [0110] and the auto

CH6, CH5, CH4, CH3, CH2, CH1, CH0, CH6, CH5, ...

MUX Register: ( Bit8 ~ Bit5)

The converted A/D channel is controlled by the register MUX, the format of MUX is show as table below.

Bit | Bit | Bit | Bit | Channel No. |

8 | 7 | 6 | 5 |

|

M | M | M | M |

|

3 | 2 | 1 | 0 |

|

0 | 0 | 0 | 0 | CH0 |

0 | 0 | 0 | 1 | CH1 |

0 | 0 | 1 | 0 | CH2 |

... | ... | ... | ... | ... |

1 | 1 | 1 | 0 | CH14 |

1 | 1 | 1 | 1 | CH15 |

Note :

∙Gain: ( Bit12 ~ Bit9)