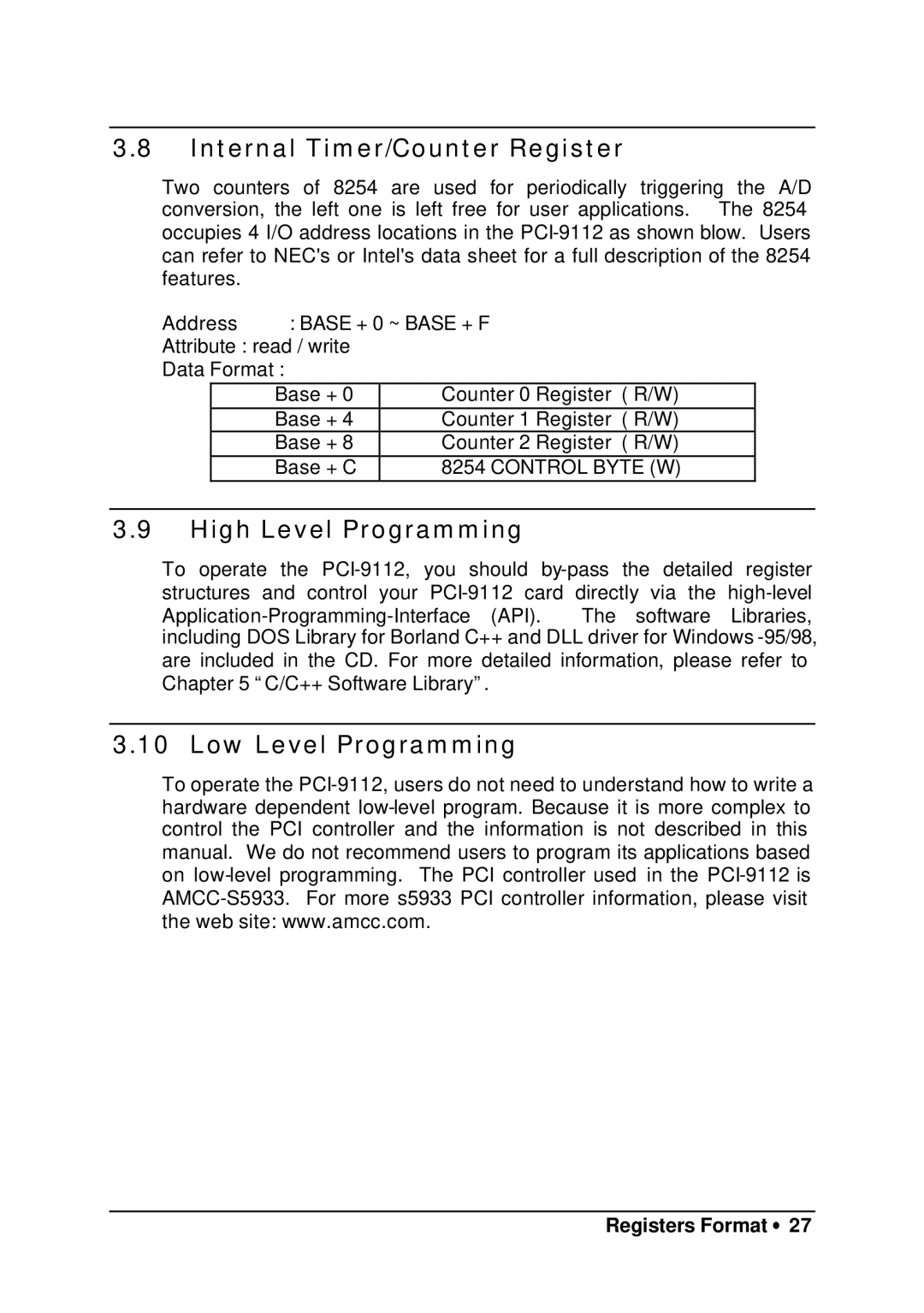

3.8Internal Timer/Counter Register

Two counters of 8254 are used for periodically triggering the A/D conversion, the left one is left free for user applications. The 8254 occupies 4 I/O address locations in the PCI-9112 as shown blow. Users can refer to NEC's or Intel's data sheet for a full description of the 8254 features.

Address | : BASE + 0 ~ BASE + F |

Attribute : read / write | |

Data Format : | |

| | | |

| | Base + 0 | Counter 0 Register ( R/W) |

| | Base + 4 | Counter 1 Register ( R/W) |

| | Base + 8 | Counter 2 Register ( R/W) |

| | Base + C | 8254 CONTROL BYTE (W) |

3.9High Level Programming

To operate the PCI-9112, you should by-pass the detailed register structures and control your PCI-9112 card directly via the high-level

Application-Programming-Interface (API). The software Libraries, including DOS Library for Borland C++ and DLL driver for Windows -95/98, are included in the CD. For more detailed information, please refer to Chapter 5 “C/C++ Software Library”.

3.10 Low Level Programming

To operate the PCI-9112, users do not need to understand how to write a hardware dependent low-level program. Because it is more complex to control the PCI controller and the information is not described in this manual. We do not recommend users to program its applications based on low-level programming. The PCI controller used in the PCI-9112 is AMCC-S5933. For more s5933 PCI controller information, please visit the web site: www.amcc.com.

Registers Format ∙ 27