Intel Server Board SE7221BK1-E

Revision

SE7221BK1-ETechnical Product Specification

Date Revision Modifications Number

Disclaimers

SE7221BK1-E Technical Product Specification

Table of contents

Acpi Implementation

Connectors

Configuration Jumpers

Bios Setup Utility

Hardware Monitoring

SE7221BK1 -E Technical Product Specification

Boot Block Post Progress Codes Power Information

Absolute Maximum Ratings

Glossary

Industry Canada ICES-003

Viii

List of Tables

SE7221BK1-E Technical Product Specification

Revision

List of Figures

Page

Introduction

Server Board Overview

SE7221BK1-E Feature Set

ƒ LPC Low Pin Count bus segment with one embedded devices

ƒ USB

PCI-X 100 Slot

CPU

Processor Subsystem

Functional Architecture

Processor Support Matrix

Memory Subsystem

Interrupts and Apic

Memory Dimm Support

Memory Configuration

Memory Bank Label Definition

Location Dimm Label Channel Population Order

Intel E7221 Chipset

Throughput Level Configuration Characteristics

Supported DDR2 modules

1.1 DDR2 Configurations

Gmch Memory Architecture Overview

Graphics Memory Controller Hub Gmch

PCI Bus P32-A I/O Subsystem

3 ICH6R

USB Interface

Power Management

PCI Express* X4 Subsystem

PCI Bus Master IDE Interface

Serial Ports

Super I/O

System Health Support

Bios Flash

O Subsystem

PCI Subsystem

1.2 P32-A Arbitration

2 P32-B 66-MHz PCI-X Subsystem SE7221BK1LX sku only

2.2 P32-B Arbitration

P32-B Arbitration Connections

P64-C Configuration IDs

3 P64-C 66/100-MHz PCI-X Subsystem

3.2 P64-C Arbitration

PCI-E

NIC Connector and Status LEDs

Video Controller

Network Interface Controller NIC

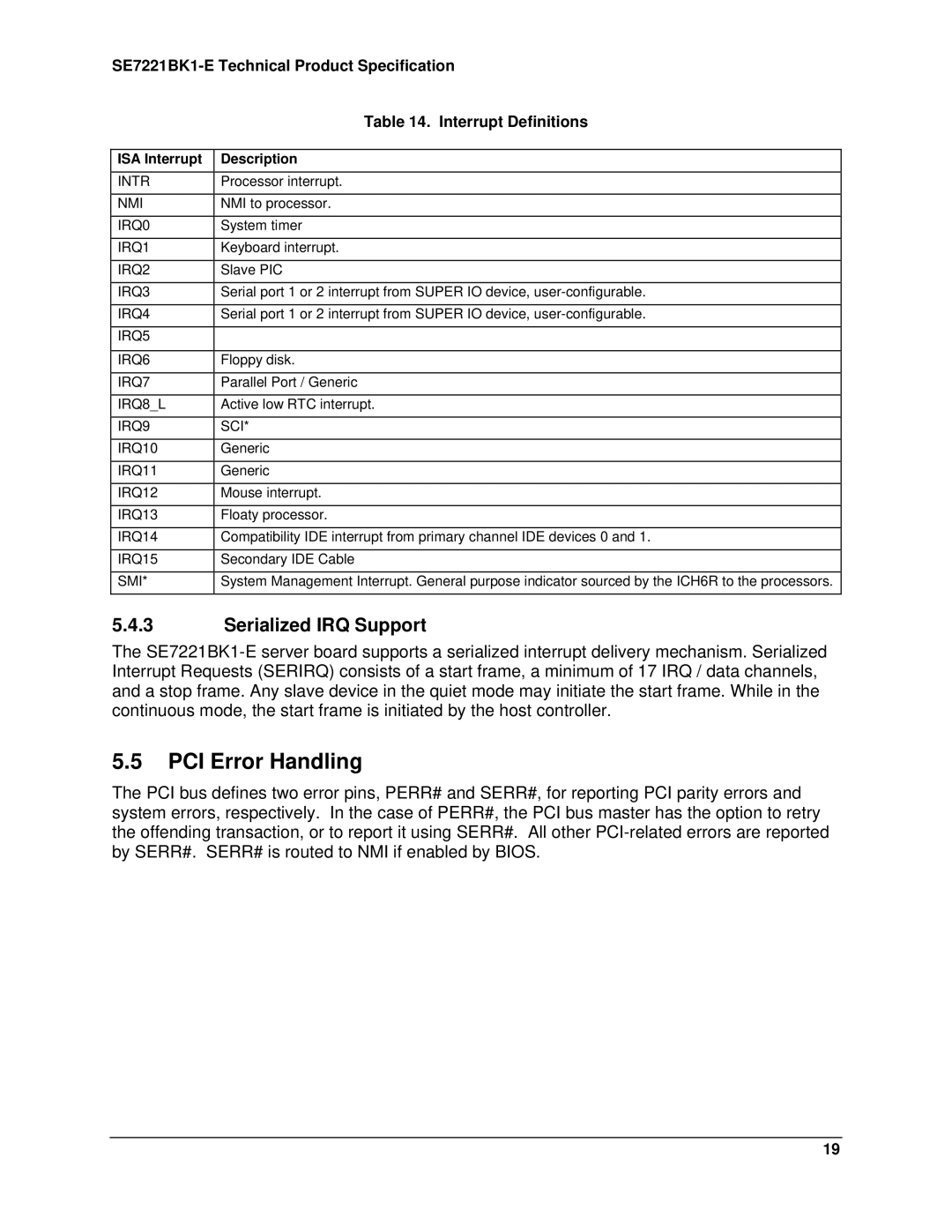

Legacy Interrupt Sources

Interrupt Routing

Legacy Interrupt Routing

Apic Interrupt Routing

Serialized IRQ Support

PCI Error Handling

ISA Interrupt Description

ICH6 Ioapic DMI Interface

ICH6

Gmch Intr CPU

PCI Interface

Super I/O

PB IRQ8 Interface

PA IRQ8 Interface

Acpi Implementation

Front Panel Switches

Acpi

USB

Power Button On to Off Legacy Power Button On to Off Acpi

Wake up Sources Acpi and Legacy

Supported Wake Events

Auxiliary CPU Power Connector Pin-out CN4B1

Connectors

Main Power Connector

Power Connector Pin-out CN4H1

LCD Header Pin-out J1C1

Front Panel Connector

I2C Header

Hsbp Header Pin-out J1D1

NIC1-82541PI10/100/1000 Connector Pin-out J5A1

VGA Connector

NIC Connector

VGA Connector Pin-out J8A1

IDEA1 Diag IDEA0 IDEA2 IDEDCS0# IDEDCS1# IDEHDACT# GND

IDE Connector

NIC2-82541PI 10/100/1000 Connector Pin-out J6A1

ATA 40-pin Connector Pin-out J3J1

USB Connectors Pin-out J5A1

Sata Connector

USB Connector

Sata Connector Pin-out J1G1, J1G2, J1J2, J2J1

External DB9 Serial a Port Pin-out J8A1

Floppy Connector

Serial Port Connector

Legacy 34-pin Floppy Connector Pin-out JP3J1

Fan Header

Keyboard and Mouse Connector

Keyboard and Mouse PS/2 Connectors Pin-out KM9A1

Miscellaneous Headers

HDD LED Header

Intrusion Cable Connector

Intrusion Cable Connector J1A1Pin-Out Pin Signal Name

HDD LED Header J1E1 Pin-Out Pin Signal Name

System Recovery and Update Jumper Options

Configuration Jumpers

System Recovery and Update Jumpers

Rolling Bios selection header

Localization

Bios Setup Utility

Configuration Reset

Keyboard Commands

Post

Load Setup Defaults?

Cancel

ESC

Feature Options Help Text Description

Entering Bios Setup

Bios Setup, Main Menu Options

Save configuration changes and exit setup?

Advanced menu

Processor configuration sub-menu

Bios Setup, Advanced Menu Options

Bios Setup, Processor configuration sub-menu options

Compatible

IDE configuration sub-menu

Bios Setup IDE Configuration Menu Options

Enabled

Cdrom Armd

Bios Setup, IDE Device Configuration Sub-menu Selections

Host & Device

Auto

Bios Setup, Super I/O Configuration Sub-menu

Floppy configuration sub-menu

Super I/O configuration sub-menu

Bios Setup, Floppy Configuration Sub-menu Selections

Bios Setup, USB Configuration Sub-menu Selections

USB configuration sub-menu

Cdrom

PCI configuration sub-menu

Bios Setup, PCI Configuration Sub-menu Selections

FDD

Bios Setup, Boot Menu Selections

Boot menu

Memory configuration sub-menu

Bios Setup, Memory Configuration Sub-menu Selections

Bios Setup, Boot Device Priority Sub-menu Selections

Boot settings configuration sub-menu selections

Boot device priority sub-menu selections

Bios Setup, Boot Settings Configuration Sub-menu Selections

Chipset Menu

North Bridge Chipset Configuration

Bios Setup, Removable Drives Sub-menu Selections

Bios Setup, Atapi Cdrom Drives Sub-menu Selections

Dram Clocks

South Bridge Chipset Configuration

Enabled, 8MB

Feature Options Help Text

Bios Setup, Security Menu Options

PXH Bridge Configuration

Security menu

Server menu

Bios Setup, Server Menu Selections

Minute

Stay On

Bios Setup, System Management Sub-menu Selections

System management sub-menu selections

Stays Off

Bios Setup, Event Log Configuration Sub-menu Selections

Serial Console features sub-menu selections

Event Log configuration sub-menu selections

Bios Setup Serial Console Features Sub-menu Selections

Bios Setup, Exit Menu Selections

Upgrading the Bios

Preparing for the Upgrade

Recording the Current Bios Settings

Flash Update Utility

Obtaining the Upgrade Utility Creating a Bootable Diskette

Rolling Bios and On-line updates

Flash Architecture and Flash Update Utility

\split AMIBOOT.ROM Amiboot

Recovery Mode

Bios Recovery

Multi-Disk Recovery

Summary of Beep codes

Manually Recovering the Bios

Beeps Error Message Post Progress Code Description

Error Handling and Reporting

Post Error Beep Codes

Post Error Beep Codes

Pmmmemallocerr

Bios Event Log

Post Error Messages and Handling

Error Code Error Message Response

Languagemoduleerr

Post Progress Codes and Messages

Post Code Checkpoints

Post Code Checkpoints

Enable IRQ-0 in PIC for system timer interrupt

Initializes remaining option ROMs

Bootblock Initialization Code Checkpoints

Boot Block Initialization Code Checkpoints

Bootblock Recovery Code Checkpoints

Boot Block Recovery Code Checkpoints

Acpi Runtime Checkpoints

DIM Code Checkpoints

Acpi Runtime Checkpoints

DIM Code Checkpoints

Post Progress Code LED Example

Diagnostic LEDs

Diagnostic LED Post Progress Codes

Boot Block Post Progress Codes

Post Progress Codes

SE7221BK1-ETechnical Product Specification

SE7221BK1-E Technical Product Specification

Power Supply Rail Voltages Units Watts

Power Information

Intel Server Board SE7221BK1-E Power Budget

Board Power Budget

5VSB output voltage rise time shall be from 1.0ms to 25.0ms

Power Supply Specifications

Power Timing Requirements

Board Power Supply Voltage Specification

Output Voltage Timing Turn On/Off Timing

Transient Load Requirements

Dynamic Loading

+5VSB

AC Line Sag Transient Performance

AC Line Transient Specification

AC Line Fast Transient EFT Specification

Absolute Maximum Ratings

Monitored Components

Hardware Monitoring

Mean Time Between Failures Mtbf Test Results

Monitored Components

FANIN7 PIN #9

Temperature

HTHEMPDA/C

Fan Speed Control

Fan Speed Control Block Diagram

Product EMC Compliance

Product Safety Compliance

Product Regulatory Compliance

Chassis Intrusion

FCC USA

Electromagnetic Compatibility Notices

Taiwan Declaration of Conformity

Europe CE Declaration of Conformity

Korean RRL Compliance

Australia / New Zealand

Replacing the Back-Up Battery

Mtbf Data

Mechanical Specifications

Product Code Calculated Mtbf Operating Temperature

Calculated Mean Time Between Failures Mtbf

SE7221BK1-E Server Board Mechanical Drawing

Sku 1 Pedestal mount I/O shield mechanical drawing Revision

Sku 2 Pedestal mount I/O shield mechanical drawing

Page

Term Definition

Glossary SE7221BK1-E Technical Product Specification

Mtbf

LPC

MBE

MSB

ZCR

SE7221BK1-E Technical Product Specification Glossary

VGA

VID