MPS Revision

This field allows you to select which MPS

APIC ACPI SCI IRQ

This field is used to enable or disable the APIC (Advanced Programmable Interrupt Controller). Due to compliance to PC2001 design guide, the system is able to run in APIC mode. Enabling APIC mode will expand available IRQs resources for the system. Settings: [Enabled], [Disabled].

CPU L1 & L2 Cache

Cache memory is additional memory that is much faster than conventional DRAM (system memory). When the CPU requests data, the system transfers the requested data from the main DRAM into cache memory, for even faster access by the CPU. The settings enable/disable the internal cache (also known as L1 or level 1 cache) and external cache (also known as L2 or level 2 cache). Setting options: [Enabled], [Disabled].

System BIOS Cacheable

Selecting [Enabled] allows caching of the system BIOS ROM at

memory area, a system error may result. Setting options: [Enabled], [Disabled].

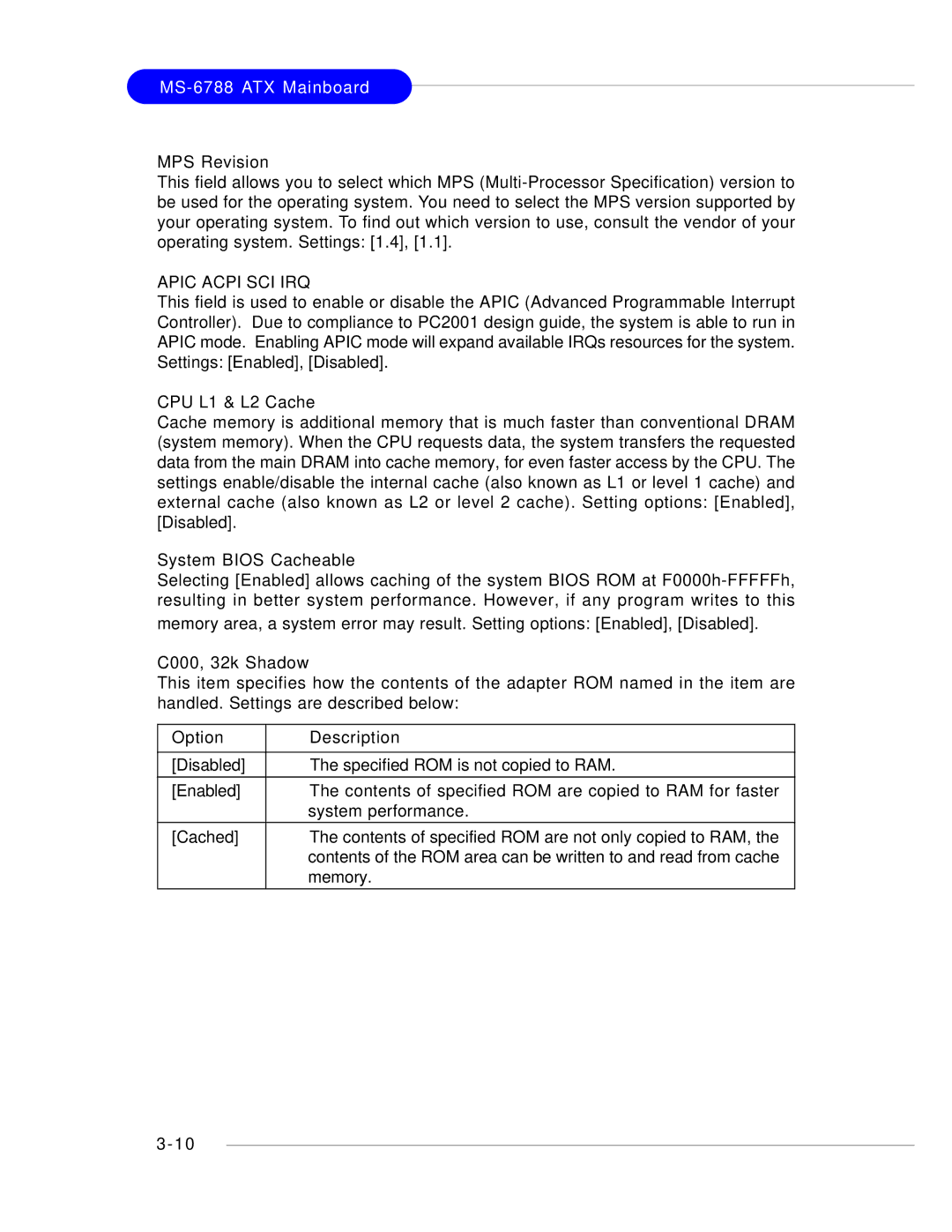

C000, 32k Shadow

This item specifies how the contents of the adapter ROM named in the item are handled. Settings are described below:

Option | Description |

|

|

[Disabled] | The specified ROM is not copied to RAM. |

[Enabled] | The contents of specified ROM are copied to RAM for faster |

| system performance. |

[Cached] | The contents of specified ROM are not only copied to RAM, the |

| contents of the ROM area can be written to and read from cache |

| memory. |