AR-B1570 User’s Guide

2. SYSTEM CONTROLLER

This chapter describes the main structure of the AR-B1570 CPU board. The following topics are covered:

!Microprocessors

!DMA Controller

!Keyboard Controller

!Interrupt Controller

!Serial Port

!Parallel Port

2.1MICROPROCESSOR

The AR-B1570 uses the NS GEODE GX1 CPU, it is an advanced 32-bit x86 compatible processor offering high performance, fully accelerated 2D graphics, a 64-synchronous DRAM controller and a PCI bus controller, all on a single chip. This latest generation of the MediaGX processor enables a new class of premium performance notebook/desktop, and IPC computer designs.

The MediaGX MMX enhanced processor companion chips provide advanced video and audio functions and permit direct interface to memory. This high-performance 64-bit processor is x86 instruction set compatible and supports MMX technology.

This processor is the latest member of the NS MediaGX family, offering high performance, fully accelerated 2D graphics, synchronous memory interface and a PCI bus controller, all on a single chip. As described in separate manuals, the CS5520 and the CS5530 I/O Companion chips fully enable the features of the MediaGX processor with MMX support. These features include full VGA and VESA video, 16-bit stereo sound, IDE interface, ISA interface, SMM power management, and AT compatibility logic. In addition, the newer CS5530 provides an Ultra DMA/33 interface, MPEG2 assist, and is AC97 Version 2.0 audio compliant.

In addition to the advanced CPU features, the MediaGX processor integrates a host of functions, which are typically implemented with external components. A full-function graphics accelerator provides pixel processing and rendering functions.

The NS MediaGX MMX-Enhanced Processor represents a new generation of x86-compatible 64-bit microprocessors with sixth-generation features. The decoupled load/store unit (within the memory management unit) allows multiple instructions in a single clock cycle. Other features include single-cycle execution, single-cycle instruction decode, 16KB write-back cache, and clock rates up to 266MHz. These features are possible by the use of advanced-process technologies and super pipelining.

2.2 DMA CONTROLLER

The equivalent of two 8237A DMA controllers are implemented on the AR-B1570 board. Each controller is a four- channel DMA device that will generate the memory addresses and control signals necessary to transfer information directly between a peripheral device and memory. This allows high-speed information transfer with less CPU intervention. The two DMA controllers are internally cascaded to provide four DMA channels for transfers to 8-bit peripherals (DMA1) and three channels for transfers to 16-bit peripherals (DMA2). DMA2 channel 0 provides the cascade interconnection between the two DMA devices, thereby maintaining IBM PC/AT compatibility.

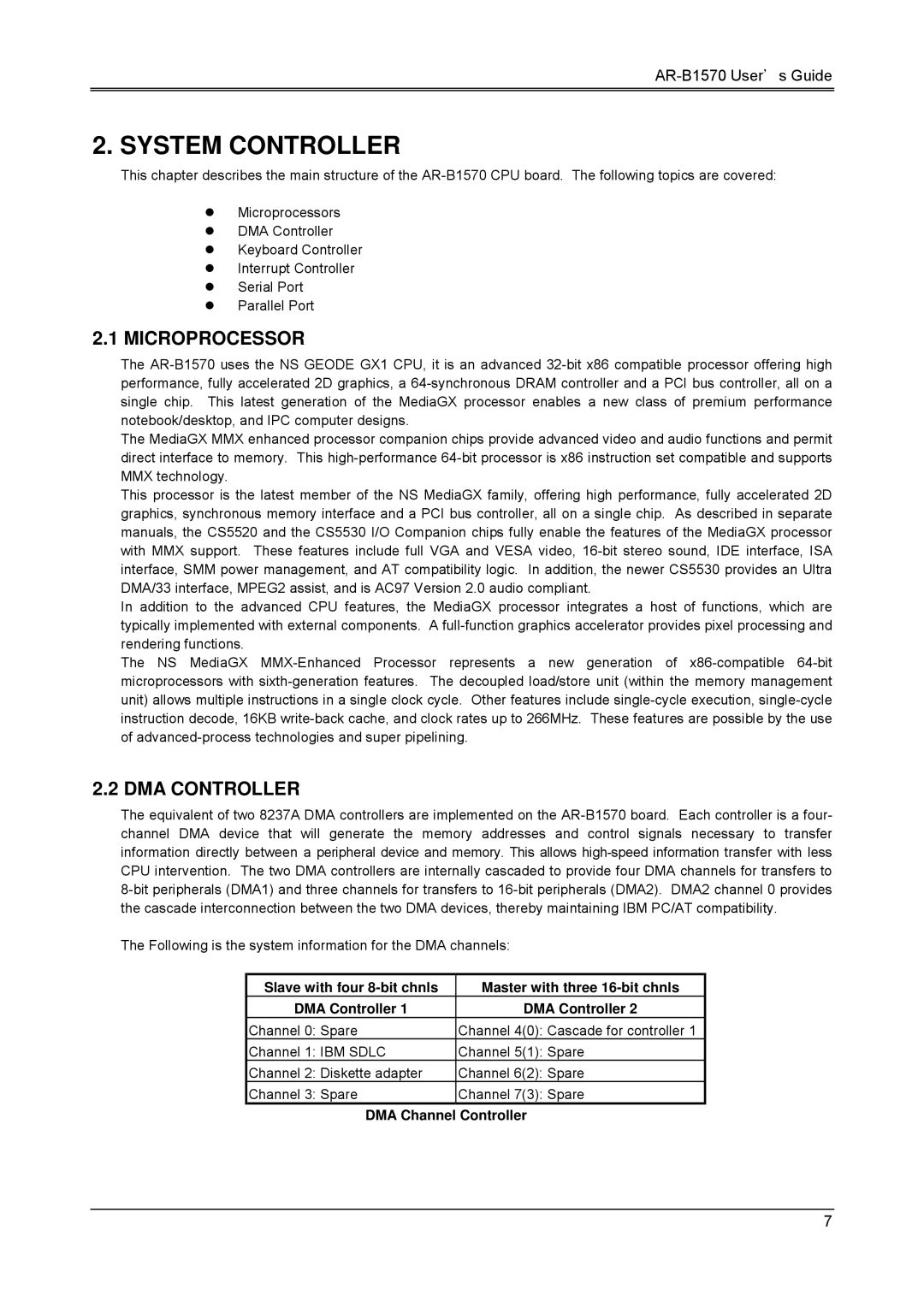

The Following is the system information for the DMA channels:

Slave with four 8-bit chnls | Master with three 16-bit chnls |

DMA Controller 1 | DMA Controller 2 |

Channel 0: Spare | Channel 4(0): Cascade for controller 1 |

Channel 1: IBM SDLC | Channel 5(1): Spare |

Channel 2: Diskette adapter | Channel 6(2): Spare |

Channel 3: Spare | Channel 7(3): Spare |

DMA Channel Controller