Motherboard Description |

|

The SDRAM controller interface is fully configurable through a set of control registers.

The Intel ® 815EP MCH supports industry standard

SCKE[4:0] is used in configurations requiring powerdown mode for the SDRAM.

1-6.5 AGP Interface

A single AGP connector is supported by the Intel ® 815EP MCH AGP interface. The AGP buffers operate in one of two selectable modes in one of two selectable modes in order to support the AGP Universal Connector:

1)3.3V drive, not 5 volt safe – This mode is compliant to the AGP 1.0 and 2.0 specs.

2)1.5V drive, not 3.3 volt safe – This mode is compliant with the AGP 2.0 spec.

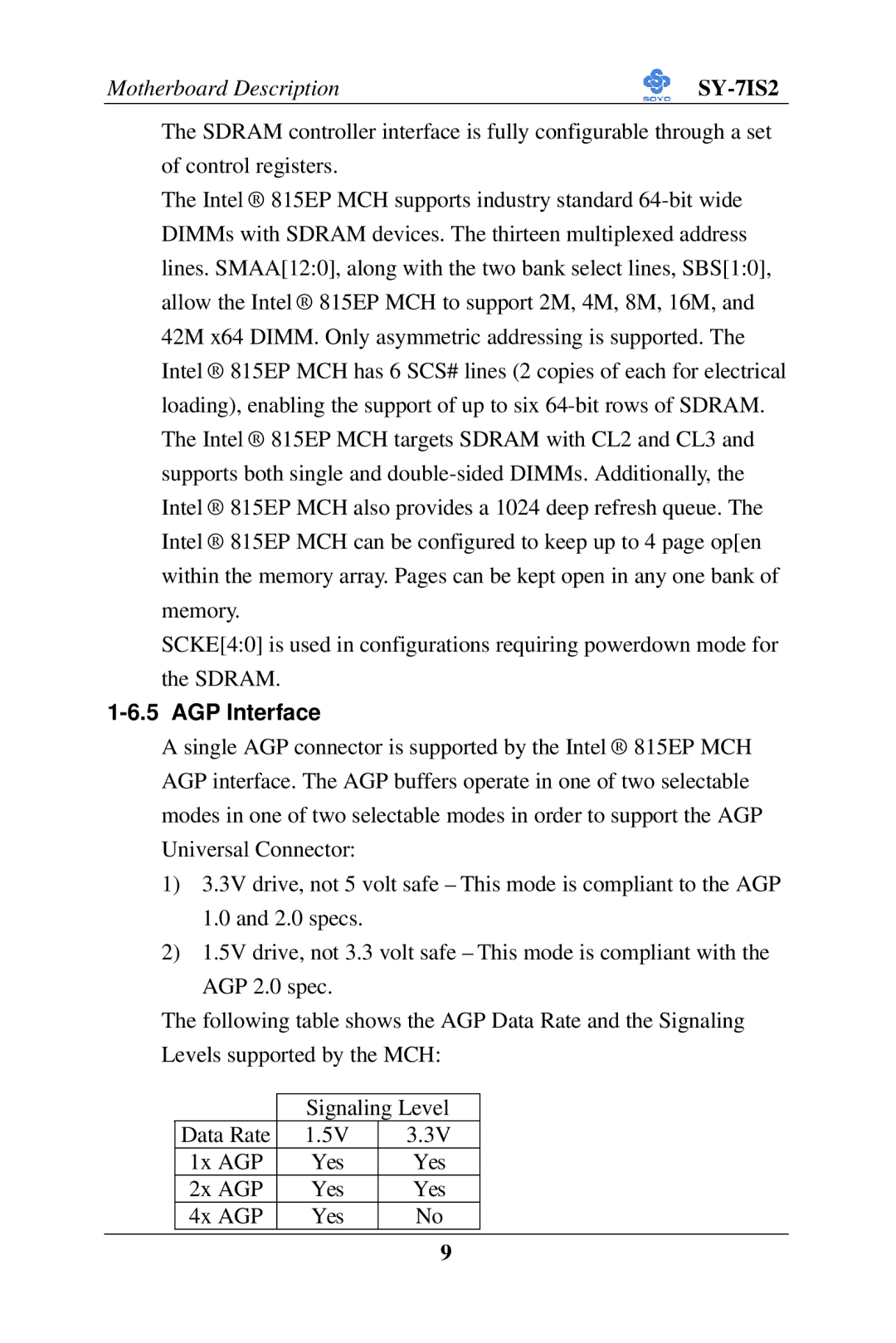

The following table shows the AGP Data Rate and the Signaling Levels supported by the MCH:

|

| Signaling Level |

| |

| Data Rate | 1.5V | 3.3V |

|

| 1x AGP | Yes | Yes |

|

| 2x AGP | Yes | Yes |

|

| 4x AGP | Yes | No |

|

|

|

|

|

|

|

|

| 9 |

|