Detailed Description

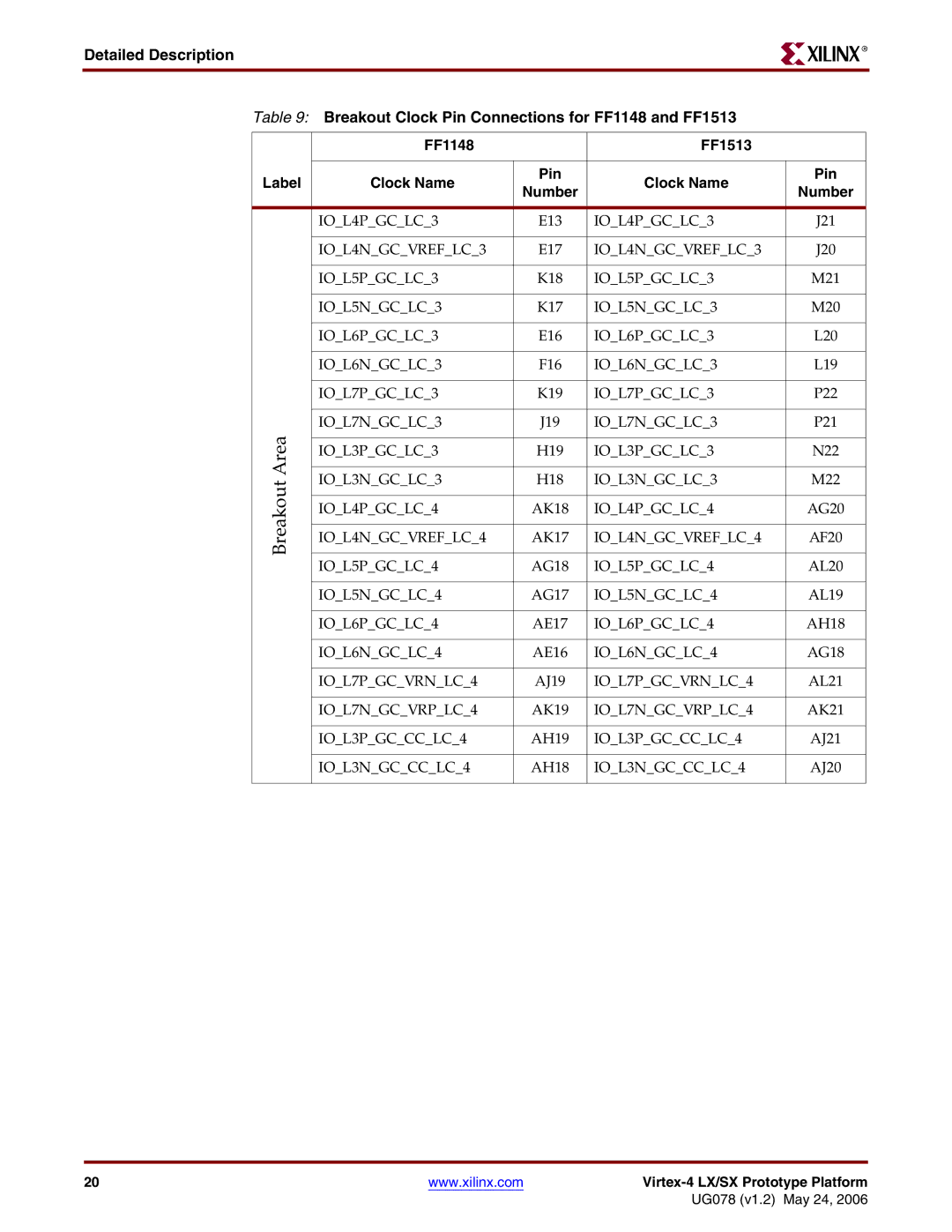

Table 9: Breakout Clock Pin Connections for FF1148 and FF1513

R

| FF1148 |

| FF1513 |

| |

|

|

|

|

| |

Label | Clock Name | Pin | Clock Name | Pin | |

Number | Number | ||||

|

|

| |||

|

|

|

|

| |

| IO_L4P_GC_LC_3 | E13 | IO_L4P_GC_LC_3 | J21 | |

|

|

|

|

| |

| IO_L4N_GC_VREF_LC_3 | E17 | IO_L4N_GC_VREF_LC_3 | J20 | |

|

|

|

|

| |

| IO_L5P_GC_LC_3 | K18 | IO_L5P_GC_LC_3 | M21 | |

|

|

|

|

| |

| IO_L5N_GC_LC_3 | K17 | IO_L5N_GC_LC_3 | M20 | |

|

|

|

|

| |

| IO_L6P_GC_LC_3 | E16 | IO_L6P_GC_LC_3 | L20 | |

|

|

|

|

| |

| IO_L6N_GC_LC_3 | F16 | IO_L6N_GC_LC_3 | L19 | |

|

|

|

|

| |

| IO_L7P_GC_LC_3 | K19 | IO_L7P_GC_LC_3 | P22 | |

|

|

|

|

| |

Area | IO_L7N_GC_LC_3 | J19 | IO_L7N_GC_LC_3 | P21 | |

|

|

|

| ||

IO_L3P_GC_LC_3 | H19 | IO_L3P_GC_LC_3 | N22 | ||

|

|

|

| ||

IO_L3N_GC_LC_3 | H18 | IO_L3N_GC_LC_3 | M22 | ||

Breakout | |||||

|

|

|

| ||

IO_L4P_GC_LC_4 | AK18 | IO_L4P_GC_LC_4 | AG20 | ||

|

|

|

| ||

IO_L4N_GC_VREF_LC_4 | AK17 | IO_L4N_GC_VREF_LC_4 | AF20 | ||

|

|

|

| ||

| IO_L5P_GC_LC_4 | AG18 | IO_L5P_GC_LC_4 | AL20 | |

|

|

|

|

| |

| IO_L5N_GC_LC_4 | AG17 | IO_L5N_GC_LC_4 | AL19 | |

|

|

|

|

| |

| IO_L6P_GC_LC_4 | AE17 | IO_L6P_GC_LC_4 | AH18 | |

|

|

|

|

| |

| IO_L6N_GC_LC_4 | AE16 | IO_L6N_GC_LC_4 | AG18 | |

|

|

|

|

| |

| IO_L7P_GC_VRN_LC_4 | AJ19 | IO_L7P_GC_VRN_LC_4 | AL21 | |

|

|

|

|

| |

| IO_L7N_GC_VRP_LC_4 | AK19 | IO_L7N_GC_VRP_LC_4 | AK21 | |

|

|

|

|

| |

| IO_L3P_GC_CC_LC_4 | AH19 | IO_L3P_GC_CC_LC_4 | AJ21 | |

|

|

|

|

| |

| IO_L3N_GC_CC_LC_4 | AH18 | IO_L3N_GC_CC_LC_4 | AJ20 | |

|

|

|

|

|

20 | www.xilinx.com |

|

|

| UG078 (v1.2) May 24, 2006 |