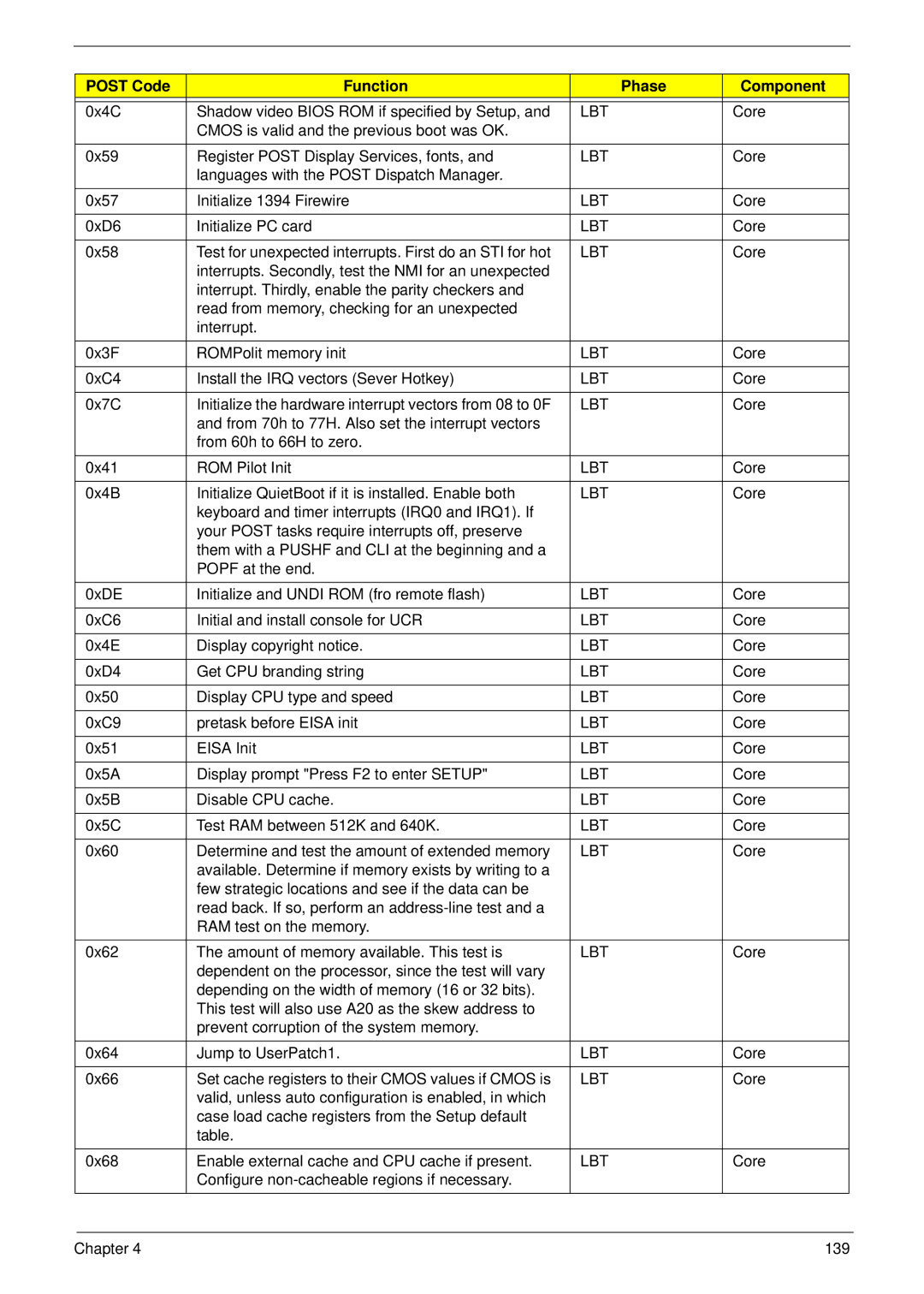

POST Code | Function | Phase | Component |

|

|

|

|

0x4C | Shadow video BIOS ROM if specified by Setup, and | LBT | Core |

| CMOS is valid and the previous boot was OK. |

|

|

|

|

|

|

0x59 | Register POST Display Services, fonts, and | LBT | Core |

| languages with the POST Dispatch Manager. |

|

|

|

|

|

|

0x57 | Initialize 1394 Firewire | LBT | Core |

|

|

|

|

0xD6 | Initialize PC card | LBT | Core |

|

|

|

|

0x58 | Test for unexpected interrupts. First do an STI for hot | LBT | Core |

| interrupts. Secondly, test the NMI for an unexpected |

|

|

| interrupt. Thirdly, enable the parity checkers and |

|

|

| read from memory, checking for an unexpected |

|

|

| interrupt. |

|

|

|

|

|

|

0x3F | ROMPolit memory init | LBT | Core |

|

|

|

|

0xC4 | Install the IRQ vectors (Sever Hotkey) | LBT | Core |

|

|

|

|

0x7C | Initialize the hardware interrupt vectors from 08 to 0F | LBT | Core |

| and from 70h to 77H. Also set the interrupt vectors |

|

|

| from 60h to 66H to zero. |

|

|

|

|

|

|

0x41 | ROM Pilot Init | LBT | Core |

|

|

|

|

0x4B | Initialize QuietBoot if it is installed. Enable both | LBT | Core |

| keyboard and timer interrupts (IRQ0 and IRQ1). If |

|

|

| your POST tasks require interrupts off, preserve |

|

|

| them with a PUSHF and CLI at the beginning and a |

|

|

| POPF at the end. |

|

|

|

|

|

|

0xDE | Initialize and UNDI ROM (fro remote flash) | LBT | Core |

|

|

|

|

0xC6 | Initial and install console for UCR | LBT | Core |

|

|

|

|

0x4E | Display copyright notice. | LBT | Core |

|

|

|

|

0xD4 | Get CPU branding string | LBT | Core |

|

|

|

|

0x50 | Display CPU type and speed | LBT | Core |

|

|

|

|

0xC9 | pretask before EISA init | LBT | Core |

|

|

|

|

0x51 | EISA Init | LBT | Core |

|

|

|

|

0x5A | Display prompt "Press F2 to enter SETUP" | LBT | Core |

|

|

|

|

0x5B | Disable CPU cache. | LBT | Core |

|

|

|

|

0x5C | Test RAM between 512K and 640K. | LBT | Core |

|

|

|

|

0x60 | Determine and test the amount of extended memory | LBT | Core |

| available. Determine if memory exists by writing to a |

|

|

| few strategic locations and see if the data can be |

|

|

| read back. If so, perform an |

|

|

| RAM test on the memory. |

|

|

|

|

|

|

0x62 | The amount of memory available. This test is | LBT | Core |

| dependent on the processor, since the test will vary |

|

|

| depending on the width of memory (16 or 32 bits). |

|

|

| This test will also use A20 as the skew address to |

|

|

| prevent corruption of the system memory. |

|

|

|

|

|

|

0x64 | Jump to UserPatch1. | LBT | Core |

|

|

|

|

0x66 | Set cache registers to their CMOS values if CMOS is | LBT | Core |

| valid, unless auto configuration is enabled, in which |

|

|

| case load cache registers from the Setup default |

|

|

| table. |

|

|

|

|

|

|

0x68 | Enable external cache and CPU cache if present. | LBT | Core |

| Configure |

|

|

|

|

|

|

Chapter 4 | 139 |