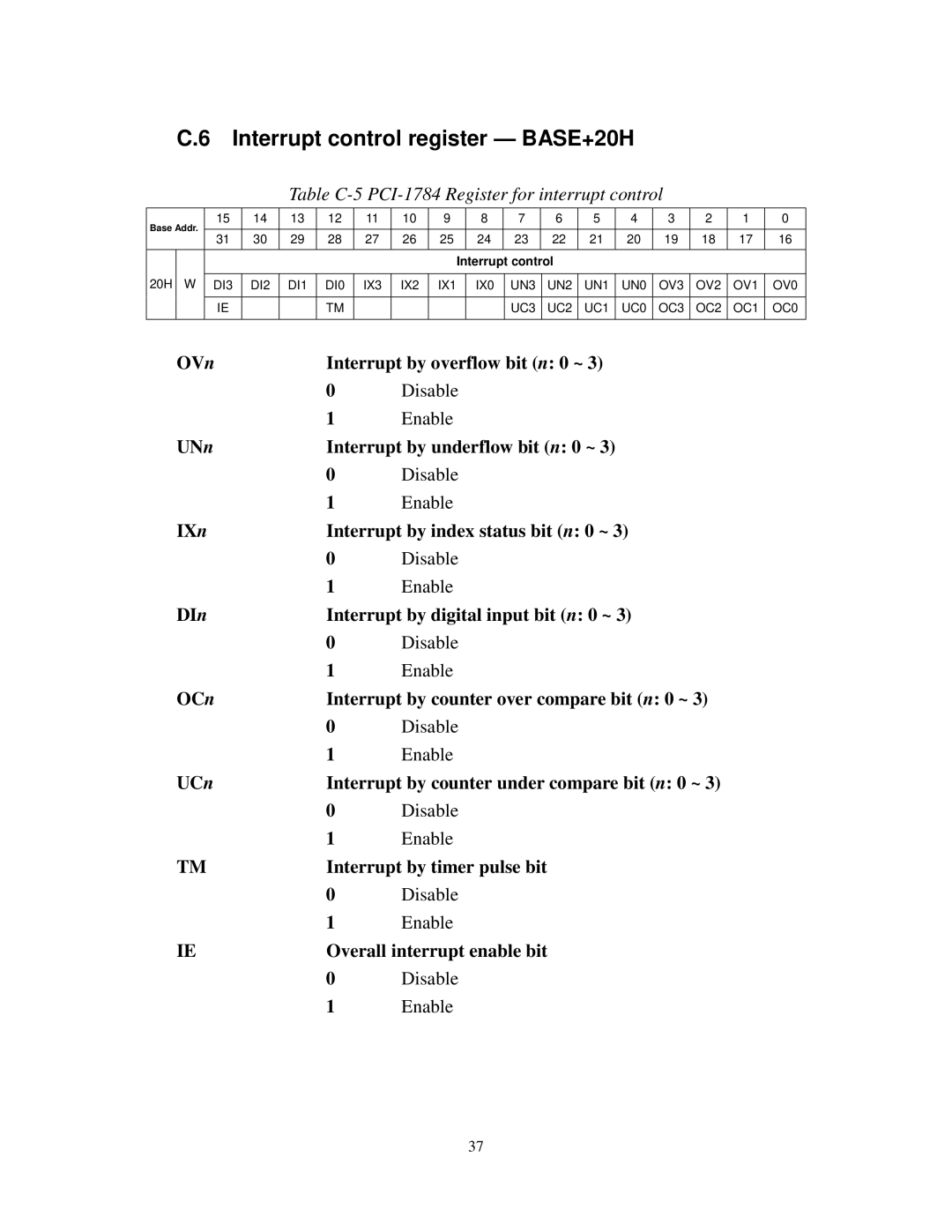

C.6 Interrupt control register — BASE+20H

Table C-5 PCI-1784 Register for interrupt control

Base Addr. | 15 | 14 | 13 | 12 | 11 | 10 | 9 |

| 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

31 | 30 | 29 | 28 | 27 | 26 | 25 |

| 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | ||

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Interrupt control |

|

|

|

|

|

| |||

20H | W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DI3 | DI2 | DI1 | DI0 | IX3 | IX2 | IX1 |

| IX0 | UN3 | UN2 | UN1 | UN0 | OV3 | OV2 | OV1 | OV0 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| IE |

|

| TM |

|

|

|

|

| UC3 | UC2 | UC1 | UC0 | OC3 | OC2 | OC1 | OC0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OVn | Interrupt by overflow bit (n: 0 ~ 3) | |

| 0 | Disable |

| 1 | Enable |

UNn | Interrupt by underflow bit (n: 0 ~ 3) | |

| 0 | Disable |

| 1 | Enable |

IXn | Interrupt by index status bit (n: 0 ~ 3) | |

| 0 | Disable |

| 1 | Enable |

DIn | Interrupt by digital input bit (n: 0 ~ 3) | |

| 0 | Disable |

| 1 | Enable |

OCn | Interrupt by counter over compare bit (n: 0 ~ 3) | |

| 0 | Disable |

| 1 | Enable |

UCn | Interrupt by counter under compare bit (n: 0 ~ 3) | |

| 0 | Disable |

| 1 | Enable |

TM | Interrupt by timer pulse bit | |

| 0 | Disable |

| 1 | Enable |

IE | Overall interrupt enable bit | |

| 0 | Disable |

| 1 | Enable |

37