to 500 KHz quadrature input frequency.

A 3600 rpm motor with 2000 ppr encoder will nave a maximum quadrature frequency of 3600×2000÷60=120 KHz. In the above example the 2 MHz sampling clock will have the noise immunity and will meet the required input frequency.

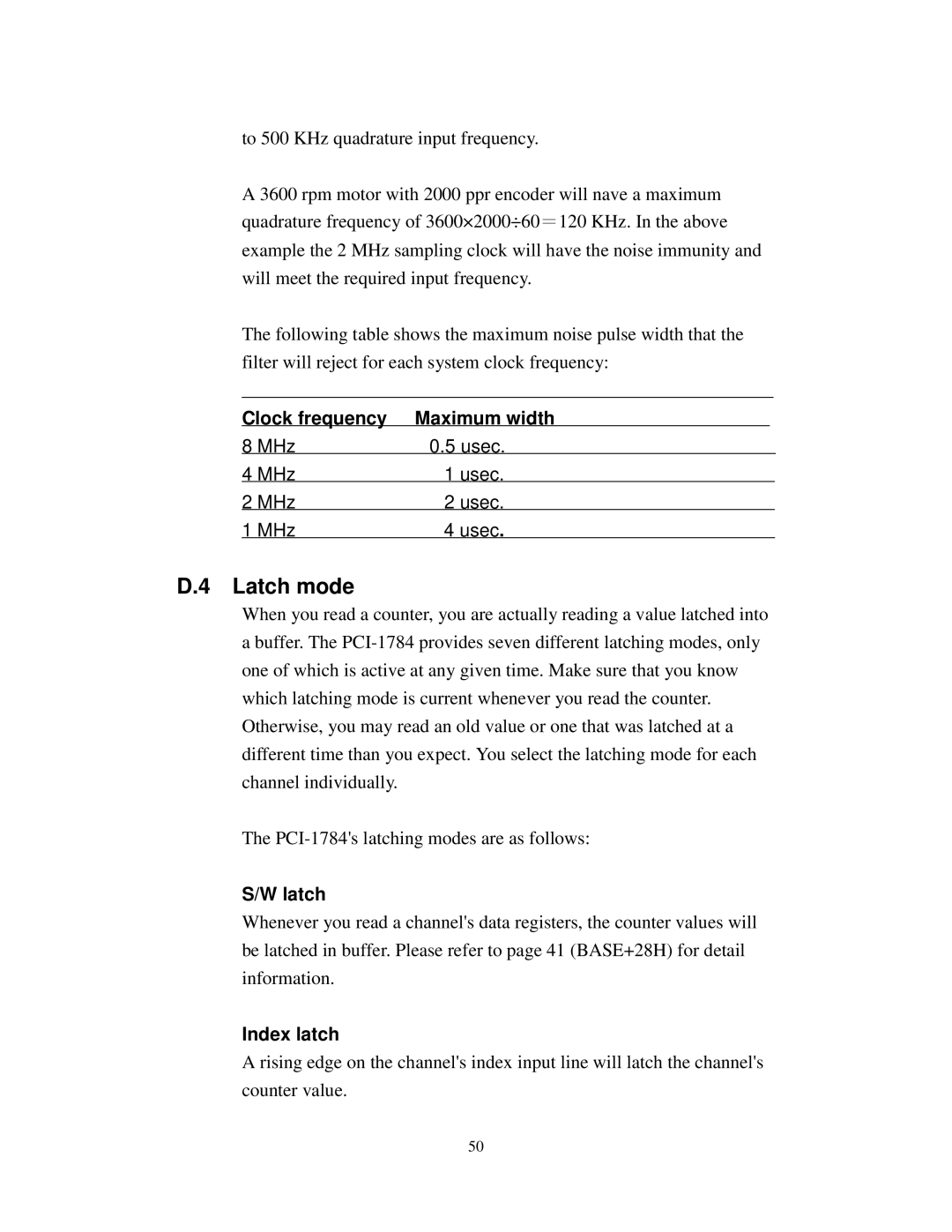

The following table shows the maximum noise pulse width that the filter will reject for each system clock frequency:

Clock frequency | Maximum width |

|

8 MHz | 0.5 usec. |

|

4 MHz | 1 usec. |

|

2 MHz | 2 usec. |

|

1 MHz | 4 usec. |

|

D.4 Latch mode

When you read a counter, you are actually reading a value latched into a buffer. The

The

S/W latch

Whenever you read a channel's data registers, the counter values will be latched in buffer. Please refer to page 41 (BASE+28H) for detail information.

Index latch

A rising edge on the channel's index input line will latch the channel's counter value.

50