9.5 Chipset Features Setup

Note: | It is strongly recommended that setup items in this | |

|

| section NOT be changed, because advanced |

|

| knowledge is required to effect such changes. |

|

|

|

|

|

|

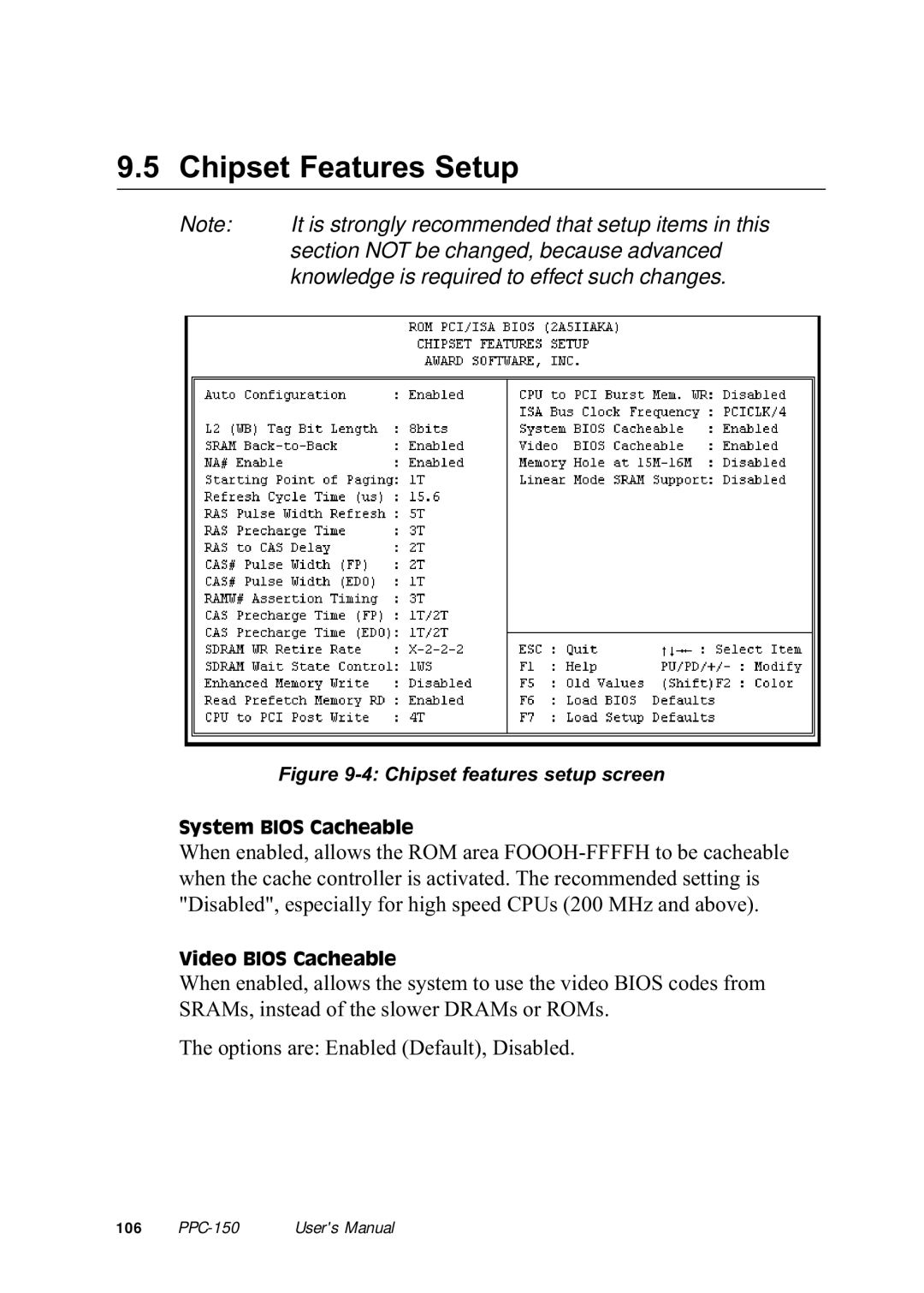

Figure 9-4: Chipset features setup screen

System BIOS Cacheable

When enabled, allows the ROM area

Video BIOS Cacheable

When enabled, allows the system to use the video BIOS codes from SRAMs, instead of the slower DRAMs or ROMs.

The options are: Enabled (Default), Disabled.

106 |

| User's Manual |