CY14B101K

1 Mbit (128K x 8) nvSRAM With Real Time Clock

Features

■25 ns, 35 ns, and 45 ns access times

■Pin compatible with STK17TA8

■Data integrity of Cypress nvSRAM combined with full featured Real Time Clock (RTC)

❐Low power, 350 nA RTC current

❐Capacitor or battery backup for RTC

■Watchdog timer

■Clock alarm with programmable interrupts

■Hands off automatic STORE on power down with only a small capacitor

■STORE to QuantumTrap™ initiated by software, device pin, or on power down

■RECALL to SRAM initiated by software or on power up

■Infinite READ, WRITE, and RECALL cycles

■High reliability

❐Endurance to 200K cycles

❐Data retention: 20 years at 55°C

■Single 3V operation with tolerance of +20%,

■Commercial and industrial temperature

■

Functional Description

The Cypress CY14B101K combines a 1 Mbit nonvolatile static RAM with a full featured real time clock in a monolithic integrated circuit. The embedded nonvolatile elements incorporate QuantumTrap technology producing the world’s most reliable nonvolatile memory. The SRAM is read and written an infinite number of times, while independent, nonvolatile data resides in the nonvolatile elements.

The Real Time Clock function provides an accurate clock with leap year tracking and a programmable high accuracy oscillator. The alarm function is programmable for one time alarm or periodic seconds, minutes, hours, or days. There is also a programmable watchdog timer for process control.

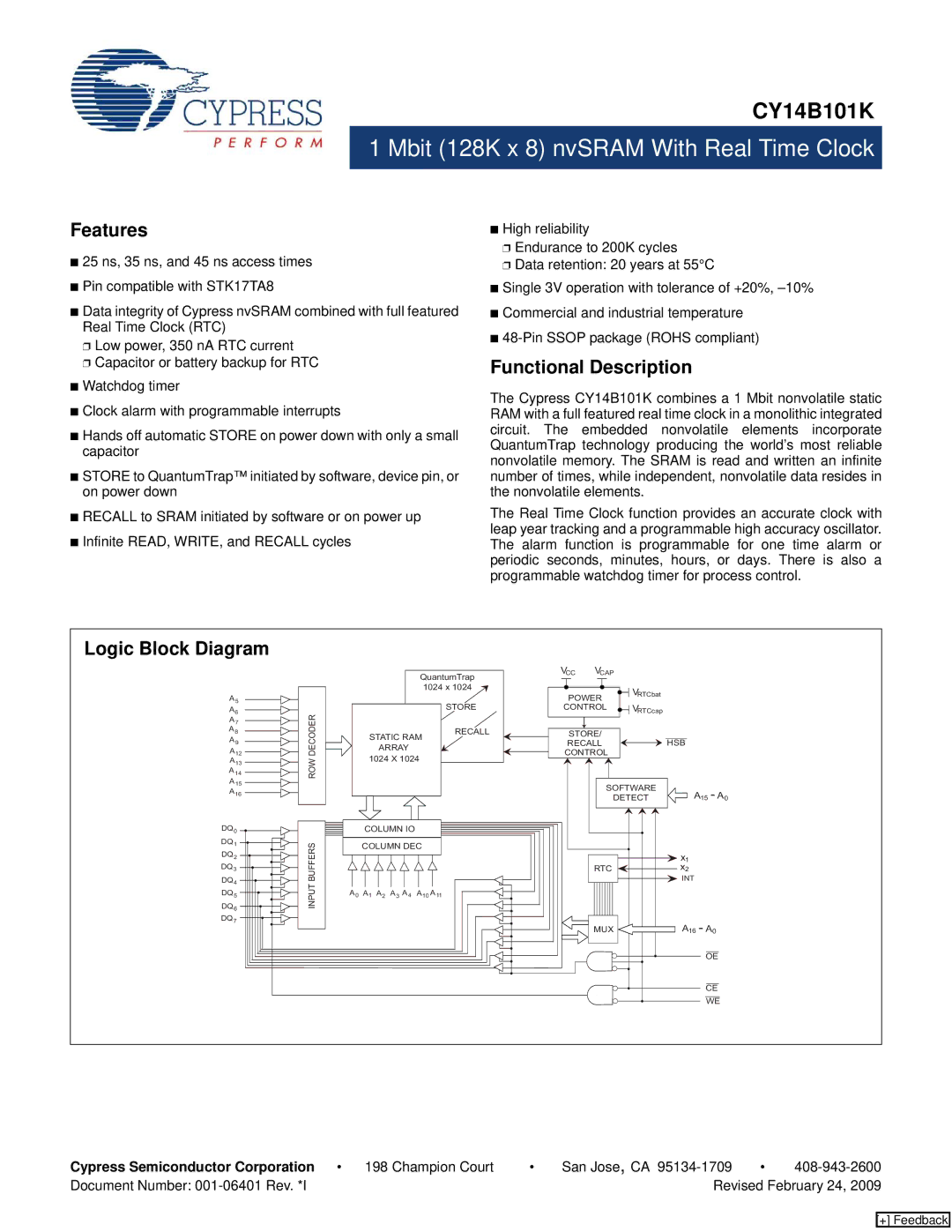

Logic Block Diagram

A5

A6

A7

A8

A9

A12

A13

A14

A15

A16

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

QuantumTrap | VCC VCAP |

|

1024 x 1024 | POWER | VRTCbat |

| ||

STORE | CONTROL | VRTCcap |

DECODER | RECALL | STORE/ |

| |

STATIC RAM | RECALL | HSB | ||

ARRAY | ||||

CONTROL |

| |||

ROW | 1024 X 1024 |

|

| |

|

|

| ||

|

| SOFTWARE | A15 - A0 | |

|

| DETECT | ||

| COLUMN IO |

|

| |

BUFFERS | COLUMN DEC |

| x1 | |

|

| |||

| RTC | x2 | ||

|

| INT | ||

INPUT | A0 A1 A2 A3 A4 A10 A11 |

|

| |

|

|

| ||

|

| MUX | A16 - A0 | |

|

|

| OE | |

|

|

| CE | |

|

|

| WE |

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised February 24, 2009 | ||

[+] Feedback