CY14B101K

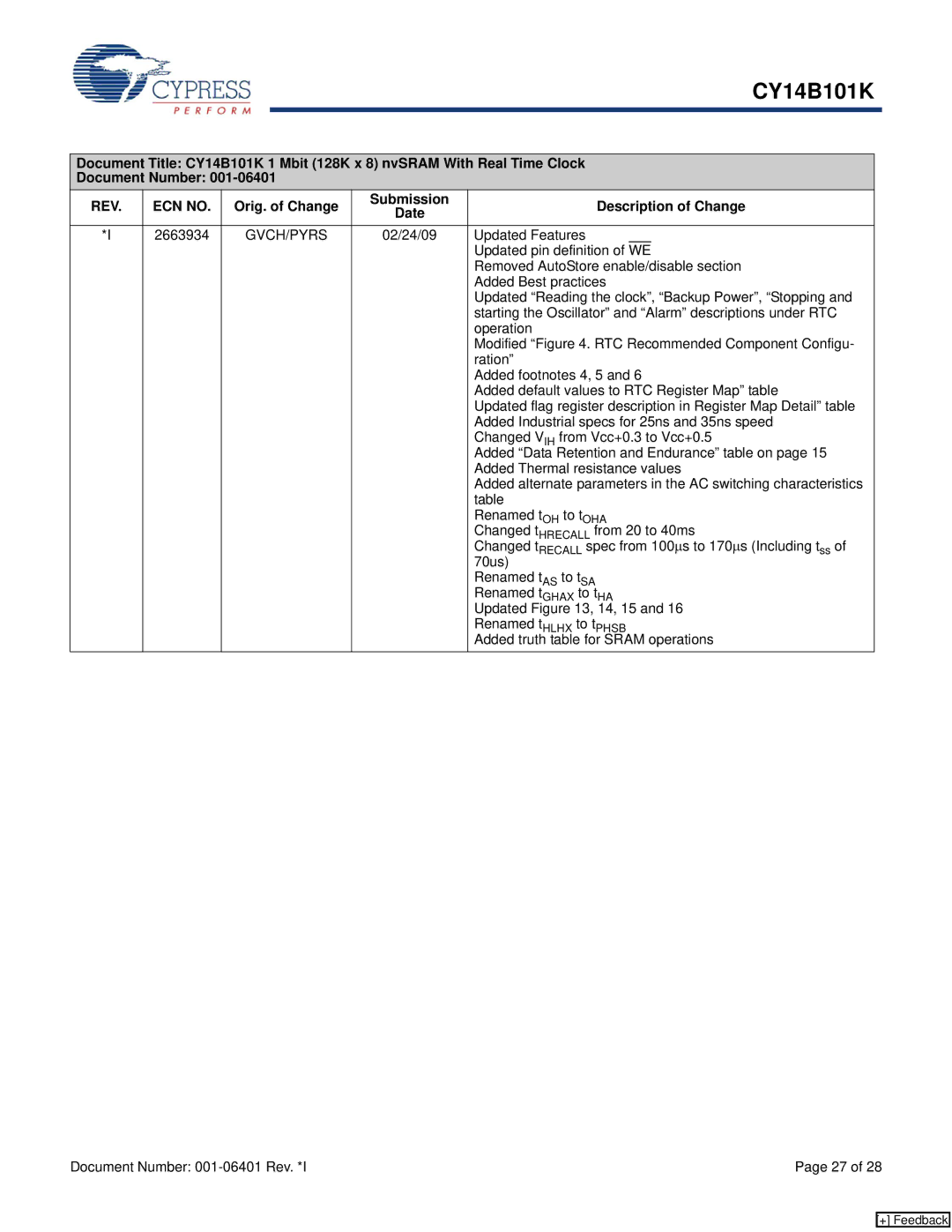

Document Title: CY14B101K 1 Mbit (128K x 8) nvSRAM With Real Time Clock

Document Number:

REV. | ECN NO. | Orig. of Change | Submission | Description of Change | |||

Date | |||||||

|

|

|

|

|

| ||

|

|

|

|

| |||

*I | 2663934 | GVCH/PYRS | 02/24/09 | Updated Features | |||

|

|

|

| Updated pin definition of | WE |

| |

|

|

|

| Removed AutoStore enable/disable section | |||

|

|

|

| Added Best practices | |||

|

|

|

| Updated “Reading the clock”, “Backup Power”, “Stopping and | |||

|

|

|

| starting the Oscillator” and “Alarm” descriptions under RTC | |||

|

|

|

| operation | |||

|

|

|

| Modified “Figure 4. RTC Recommended Component Configu- | |||

|

|

|

| ration” | |||

|

|

|

| Added footnotes 4, 5 and 6 | |||

|

|

|

| Added default values to RTC Register Map” table | |||

|

|

|

| Updated flag register description in Register Map Detail” table | |||

|

|

|

| Added Industrial specs for 25ns and 35ns speed | |||

|

|

|

| Changed VIH from Vcc+0.3 to Vcc+0.5 | |||

|

|

|

| Added “Data Retention and Endurance” table on page 15 | |||

|

|

|

| Added Thermal resistance values | |||

|

|

|

| Added alternate parameters in the AC switching characteristics | |||

|

|

|

| table | |||

|

|

|

| Renamed tOH to tOHA | |||

|

|

|

| Changed tHRECALL from 20 to 40ms | |||

|

|

|

| Changed tRECALL spec from 100μs to 170μs (Including tss of | |||

|

|

|

| 70us) | |||

|

|

|

| Renamed tAS to tSA | |||

|

|

|

| Renamed tGHAX to tHA | |||

|

|

|

| Updated Figure 13, 14, 15 and 16 | |||

|

|

|

| Renamed tHLHX to tPHSB | |||

|

|

|

| Added truth table for SRAM operations | |||

Document Number: | Page 27 of 28 |

[+] Feedback