CY7C1441AV33

CY7C1443AV33,CY7C1447AV33

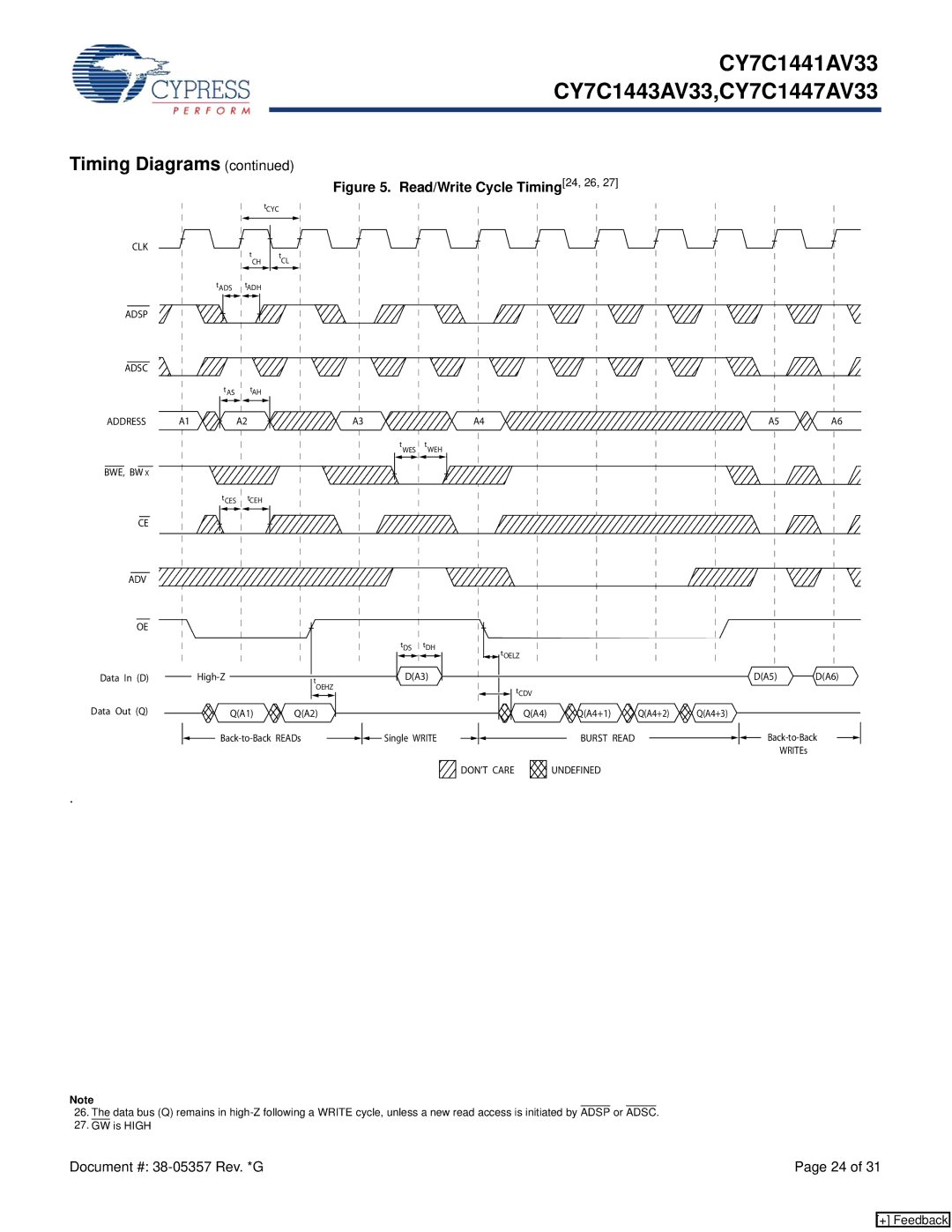

Timing Diagrams (continued)

Figure 5. Read/Write Cycle Timing[24, 26, 27]

|

|

| tCYC |

|

CLK |

| tCH | tCL |

|

|

|

| ||

| tADS | tADH |

|

|

ADSP |

|

|

|

|

ADSC |

|

|

|

|

| tAS | tAH |

|

|

ADDRESS | A1 | A2 | A3 | A4 |

|

|

| tWES | t WEH |

BWE, BW X

| tCES tCEH |

|

|

CE |

|

|

|

ADV |

|

|

|

OE |

|

|

|

|

|

| tDS tDH |

Data In (D) | t | D(A3) | |

|

| OEHZ |

|

Data Out (Q) | Q(A1) | Q(A2) |

|

| Single WRITE | ||

![]()

![]() tOELZ

tOELZ

tCDV |

|

|

|

Q(A4) | Q(A4+1) | Q(A4+2) | Q(A4+3) |

| BURST READ |

|

|

DON’T CARE | UNDEFINED |

A5A6

D(A5) D(A6)

WRITEs

.

Note

26.The data bus (Q) remains in

27.GW is HIGH

Document #: | Page 24 of 31 |

[+] Feedback