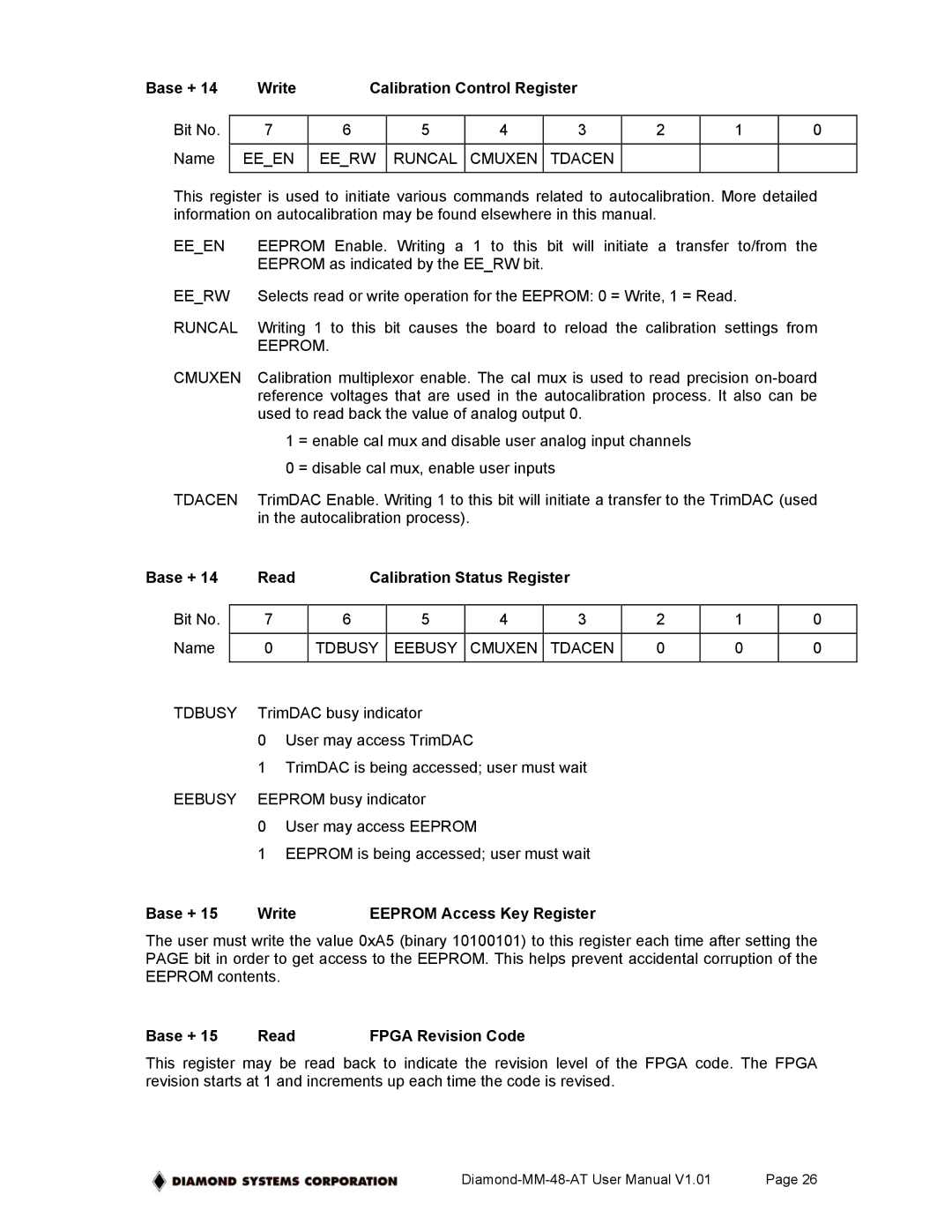

Base + 14 | Write | Calibration Control Register |

|

|

| |||

|

|

|

|

|

|

|

|

|

Bit No. | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

Name | EE_EN | EE_RW | RUNCAL | CMUXEN | TDACEN |

|

|

|

|

|

|

|

|

|

|

|

|

This register is used to initiate various commands related to autocalibration. More detailed information on autocalibration may be found elsewhere in this manual.

EE_EN | EEPROM Enable. Writing a 1 to this bit will initiate a transfer to/from the | ||||||||||

|

| EEPROM as indicated by the EE_RW bit. |

|

|

|

| |||||

EE_RW | Selects read or write operation for the EEPROM: 0 = Write, 1 = Read. |

| |||||||||

RUNCAL | Writing 1 to this bit causes the board to reload the calibration settings from | ||||||||||

|

| EEPROM. |

|

|

|

|

|

|

|

| |

CMUXEN | Calibration multiplexor enable. The cal mux is used to read precision | ||||||||||

|

| reference voltages that are used in the autocalibration process. It also can be | |||||||||

|

| used to read back the value of analog output 0. |

|

|

| ||||||

|

| 1 = enable cal mux and disable user analog input channels |

|

| |||||||

|

| 0 = disable cal mux, enable user inputs |

|

|

| ||||||

TDACEN | TrimDAC Enable. Writing 1 to this bit will initiate a transfer to the TrimDAC (used | ||||||||||

|

| in the autocalibration process). |

|

|

|

|

|

| |||

Base + 14 | Read | Calibration Status Register |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| |

Bit No. |

| 7 | 6 | 5 |

| 4 |

| 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

Name |

| 0 | TDBUSY | EEBUSY |

| CMUXEN |

| TDACEN | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

TDBUSY | TrimDAC busy indicator |

|

|

|

|

|

| ||||

0User may access TrimDAC

1TrimDAC is being accessed; user must wait

EEBUSY EEPROM busy indicator

0User may access EEPROM

1EEPROM is being accessed; user must wait

Base + 15 | Write | EEPROM Access Key Register |

The user must write the value 0xA5 (binary 10100101) to this register each time after setting the PAGE bit in order to get access to the EEPROM. This helps prevent accidental corruption of the EEPROM contents.

Base + 15 | Read | FPGA Revision Code |

This register may be read back to indicate the revision level of the FPGA code. The FPGA revision starts at 1 and increments up each time the code is revised.

Page 26 |