HP E8491A Triggering

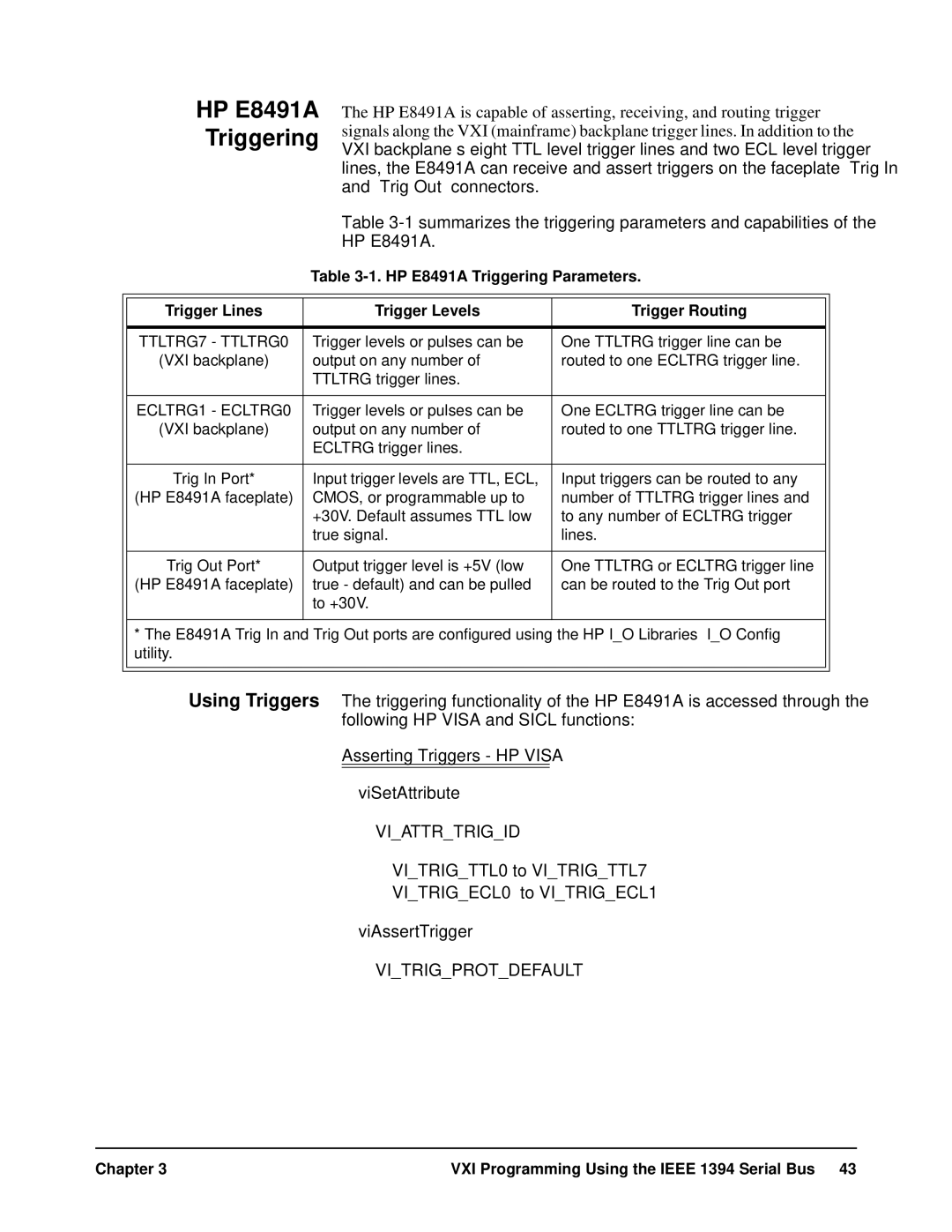

The HP E8491A is capable of asserting, receiving, and routing trigger signals along the VXI (mainframe) backplane trigger lines. In addition to the VXI backplane’s eight TTL level trigger lines and two ECL level trigger lines, the E8491A can receive and assert triggers on the faceplate ‘Trig In’ and ‘Trig Out’ connectors.

Table

Table

Trigger Lines | Trigger Levels | Trigger Routing |

|

|

|

TTLTRG7 - TTLTRG0 | Trigger levels or pulses can be | One TTLTRG trigger line can be |

(VXI backplane) | output on any number of | routed to one ECLTRG trigger line. |

| TTLTRG trigger lines. |

|

|

|

|

ECLTRG1 - ECLTRG0 | Trigger levels or pulses can be | One ECLTRG trigger line can be |

(VXI backplane) | output on any number of | routed to one TTLTRG trigger line. |

| ECLTRG trigger lines. |

|

|

|

|

Trig In Port* | Input trigger levels are TTL, ECL, | Input triggers can be routed to any |

(HP E8491A faceplate) | CMOS, or programmable up to | number of TTLTRG trigger lines and |

| +30V. Default assumes TTL low | to any number of ECLTRG trigger |

| true signal. | lines. |

|

|

|

Trig Out Port* | Output trigger level is +5V (low | One TTLTRG or ECLTRG trigger line |

(HP E8491A faceplate) | true - default) and can be pulled | can be routed to the Trig Out port |

| to +30V. |

|

|

|

|

* The E8491A Trig In and Trig Out ports are configured using the HP I_O Libraries ‘I_O Config’ utility.

Using Triggers The triggering functionality of the HP E8491A is accessed through the following HP VISA and SICL functions:

Asserting Triggers - HP VISA

viSetAttribute

VI_ATTR_TRIG_ID

VI_TRIG_TTL0 to VI_TRIG_TTL7

VI_TRIG_ECL0 to VI_TRIG_ECL1

viAssertTrigger

VI_TRIG_PROT_DEFAULT

Chapter 3 | VXI Programming Using the IEEE 1394 Serial Bus 43 |