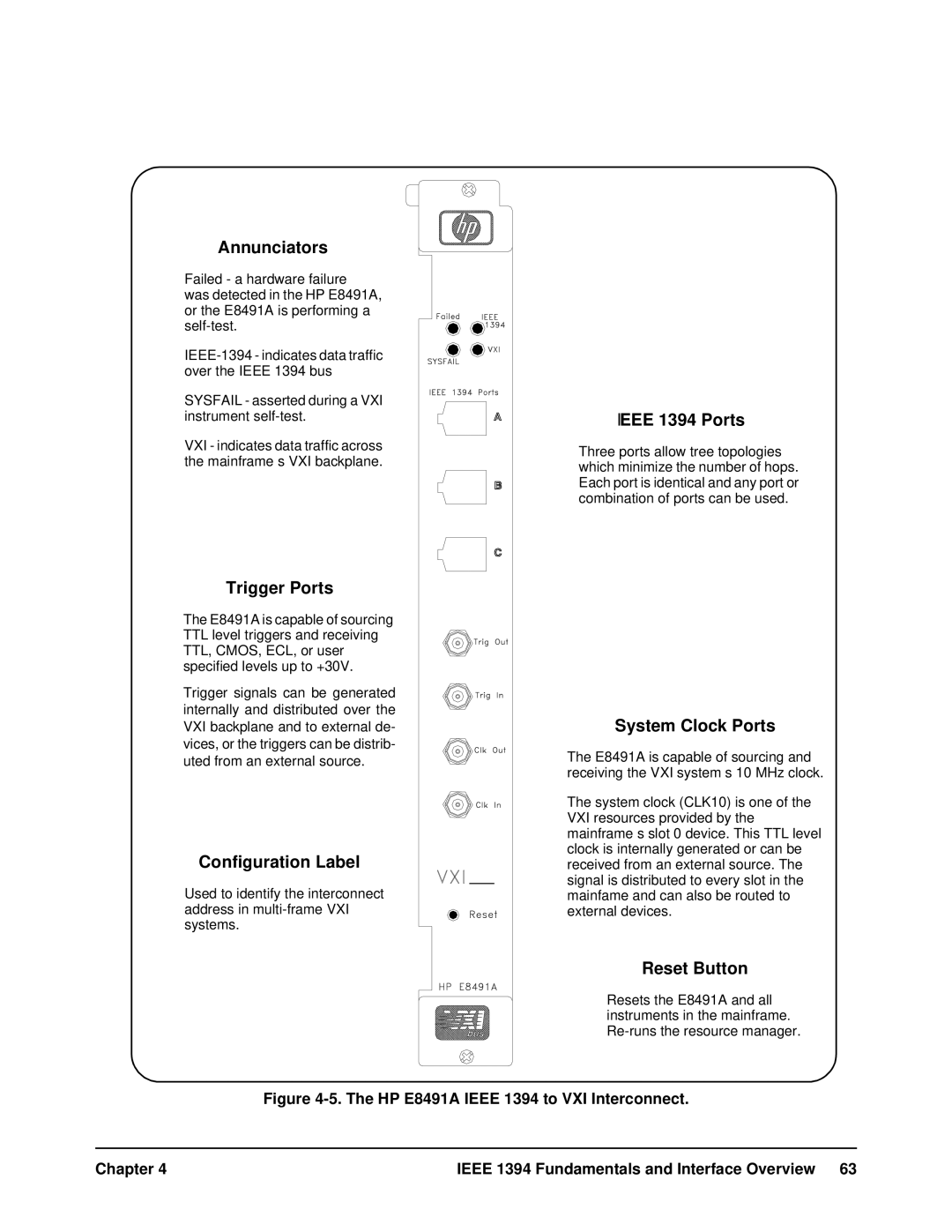

Annunciators

Failed - a hardware failure

was detected in the HP E8491A, or the E8491A is performing a

SYSFAIL - asserted during a VXI instrument

VXI - indicates data traffic across the mainframe’s VXI backplane.

Trigger Ports

The E8491A is capable of sourcing TTL level triggers and receiving TTL, CMOS, ECL, or user specified levels up to +30V.

Trigger signals can be generated internally and distributed over the VXI backplane and to external de- vices, or the triggers can be distrib- uted from an external source.

Configuration Label

Used to identify the interconnect address in

IEEE 1394 Ports

Three ports allow tree topologies which minimize the number of hops. Each port is identical and any port or combination of ports can be used.

System Clock Ports

The E8491A is capable of sourcing and receiving the VXI system’s 10 MHz clock.

The system clock (CLK10) is one of the VXI resources provided by the mainframe’s slot 0 device. This TTL level clock is internally generated or can be received from an external source. The signal is distributed to every slot in the mainfame and can also be routed to external devices.

Reset Button

Resets the E8491A and all instruments in the mainframe.

Figure 4-5. The HP E8491A IEEE 1394 to VXI Interconnect.

Chapter 4 | IEEE 1394 Fundamentals and Interface Overview 63 |