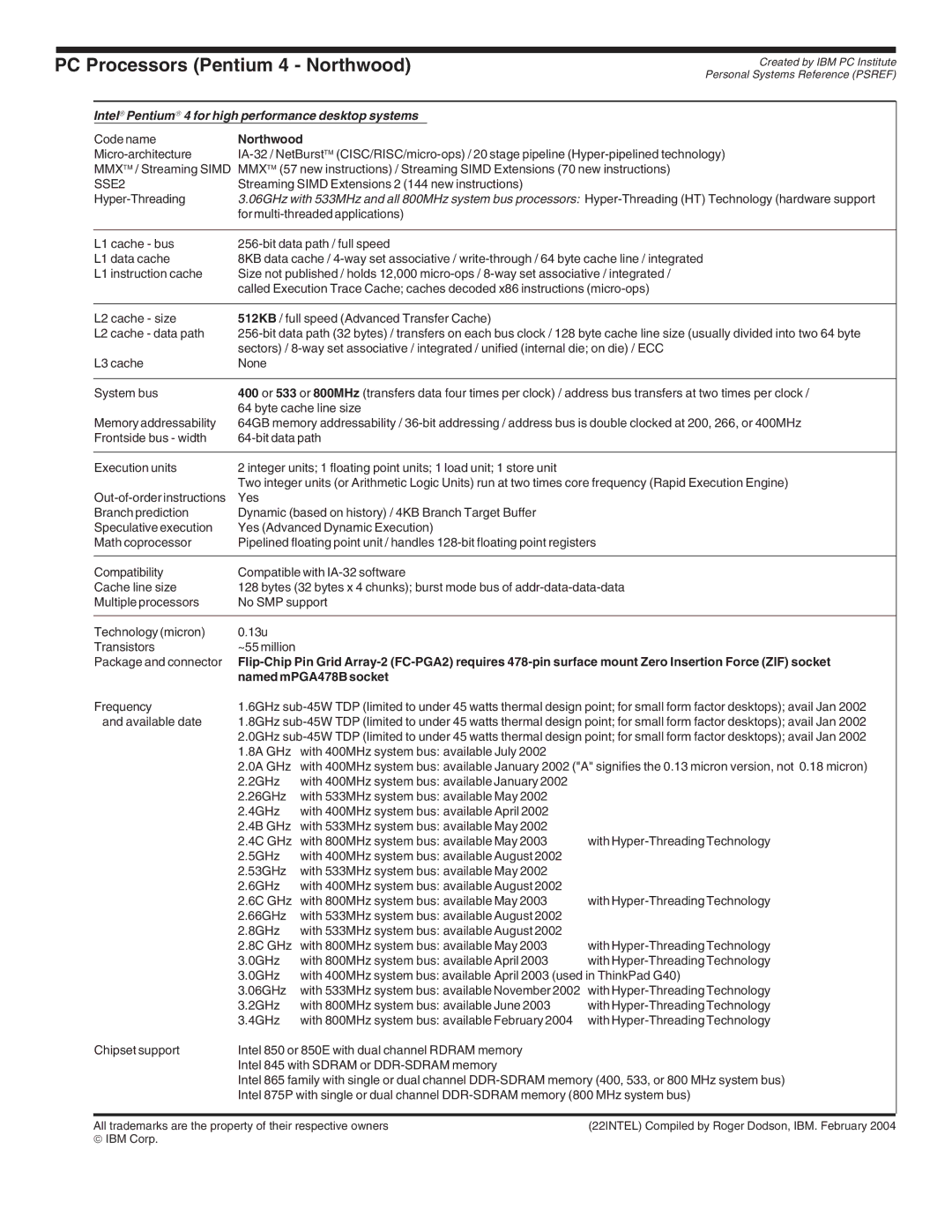

PC Processors (Pentium 4 - Northwood)

Created by IBM PC Institute Personal Systems Reference (PSREF)

Intel→ Pentium→ 4 for high performance desktop systems |

|

| ||

Code name | Northwood |

| ||

MMX™ / Streaming SIMD | MMX™ (57 new instructions) / Streaming SIMD Extensions (70 new instructions) | |||

SSE2 | Streaming SIMD Extensions 2 (144 new instructions) |

| ||

3.06GHz with 533MHz and all 800MHz system bus processors: | ||||

| for |

| ||

|

|

|

| |

L1 cache - bus |

| |||

L1 data cache | 8KB data cache / | |||

L1 instruction cache | Size not published / holds 12,000 | |||

| called Execution Trace Cache; caches decoded x86 instructions | |||

|

|

|

| |

L2 cache - size | 512KB / full speed (Advanced Transfer Cache) |

| ||

L2 cache - data path | ||||

| sectors) / | |||

L3 cache | None |

|

|

|

|

|

| ||

System bus | 400 or 533 or 800MHz (transfers data four times per clock) / address bus transfers at two times per clock / | |||

| 64 byte cache line size |

| ||

Memory addressability | 64GB memory addressability / | |||

Frontside bus - width |

| |||

|

|

| ||

Execution units | 2 integer units; 1 floating point units; 1 load unit; 1 store unit |

| ||

| Two integer units (or Arithmetic Logic Units) run at two times core frequency (Rapid Execution Engine) | |||

Yes |

|

|

| |

Branch prediction | Dynamic (based on history) / 4KB Branch Target Buffer |

| ||

Speculative execution | Yes (Advanced Dynamic Execution) |

| ||

Math coprocessor | Pipelined floating point unit / handles | |||

|

|

| ||

Compatibility | Compatible with |

| ||

Cache line size | 128 bytes (32 bytes x 4 chunks); burst mode bus of | |||

Multiple processors | No SMP support |

| ||

|

|

|

|

|

Technology (micron) | 0.13u |

|

|

|

Transistors | ~55 million |

|

|

|

Package and connector | ||||

| named mPGA478B socket |

| ||

Frequency | 1.6GHz | |||

and available date | 1.8GHz | |||

| 2.0GHz | |||

| 1.8A GHz | with 400MHz system bus: available July 2002 |

| |

| 2.0A GHz | with 400MHz system bus: available January 2002 ("A" signifies the 0.13 micron version, not 0.18 micron) | ||

| 2.2GHz | with 400MHz system bus: available January 2002 |

| |

| 2.26GHz with 533MHz system bus: available May 2002 |

| ||

| 2.4GHz | with 400MHz system bus: available April 2002 |

| |

| 2.4B GHz | with 533MHz system bus: available May 2002 |

| |

| 2.4C GHz | with 800MHz system bus: available May 2003 | with | |

| 2.5GHz | with 400MHz system bus: available August 2002 |

| |

| 2.53GHz with 533MHz system bus: available May 2002 |

| ||

| 2.6GHz | with 400MHz system bus: available August 2002 |

| |

| 2.6C GHz | with 800MHz system bus: available May 2003 | with | |

| 2.66GHz with 533MHz system bus: available August 2002 |

| ||

| 2.8GHz | with 533MHz system bus: available August 2002 |

| |

| 2.8C GHz | with 800MHz system bus: available May 2003 | with | |

| 3.0GHz | with 800MHz system bus: available April 2003 | with | |

| 3.0GHz | with 400MHz system bus: available April 2003 (used in ThinkPad G40) | ||

| 3.06GHz | with 533MHz system bus: available November 2002 | with | |

| 3.2GHz | with 800MHz system bus: available June 2003 | with | |

| 3.4GHz | with 800MHz system bus: available February 2004 | with | |

Chipset support | Intel 850 or 850E with dual channel RDRAM memory |

| ||

| Intel 845 with SDRAM or |

| ||

| Intel 865 family with single or dual channel | |||

| Intel 875P with single or dual channel | |||

|

|

|

|

|

All trademarks are the property of their respective owners | (22INTEL) Compiled by Roger Dodson, IBM. February 2004 |

♥ IBM Corp. |

|