Intel Desktop Board D865PCD Technical Product Specification

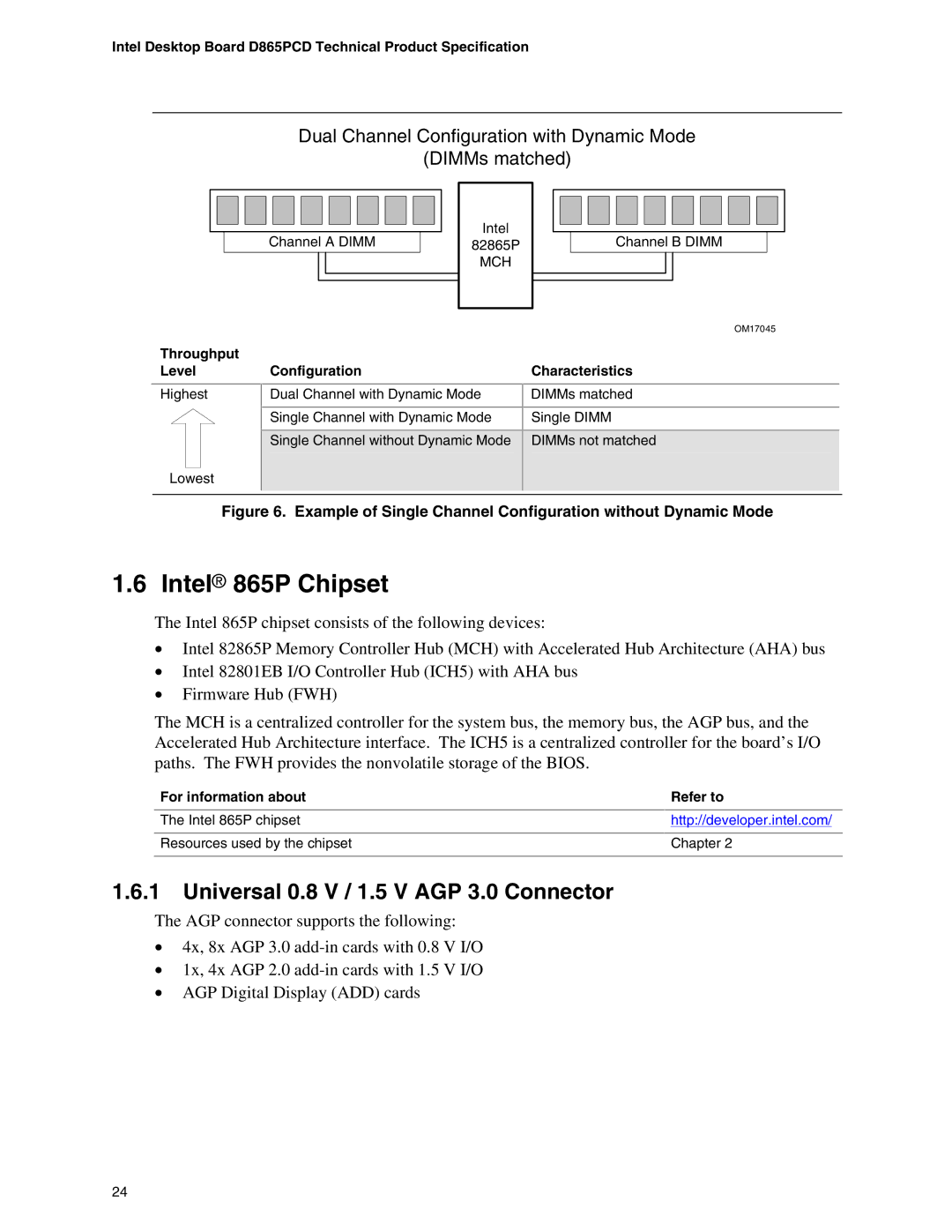

Dual Channel Configuration with Dynamic Mode

(DIMMs matched)

Channel A DIMM

Intel

82865P MCH

Channel B DIMM

Throughput Level

Highest

Configuration

Dual Channel with Dynamic Mode

Single Channel with Dynamic Mode

Single Channel without Dynamic Mode

OM17045

Characteristics

DIMMs matched

Single DIMM

DIMMs not matched

Lowest

Figure 6. Example of Single Channel Configuration without Dynamic Mode

1.6 Intel® 865P Chipset

The Intel 865P chipset consists of the following devices:

•Intel 82865P Memory Controller Hub (MCH) with Accelerated Hub Architecture (AHA) bus

•Intel 82801EB I/O Controller Hub (ICH5) with AHA bus

•Firmware Hub (FWH)

The MCH is a centralized controller for the system bus, the memory bus, the AGP bus, and the Accelerated Hub Architecture interface. The ICH5 is a centralized controller for the board’s I/O paths. The FWH provides the nonvolatile storage of the BIOS.

For information about

The Intel 865P chipset

Resources used by the chipset

Refer to

http://developer.intel.com/

Chapter 2

1.6.1Universal 0.8 V / 1.5 V AGP 3.0 Connector

The AGP connector supports the following:

•4x, 8x AGP 3.0

•1x, 4x AGP 2.0

•AGP Digital Display (ADD) cards

24