BIOS Setup Program

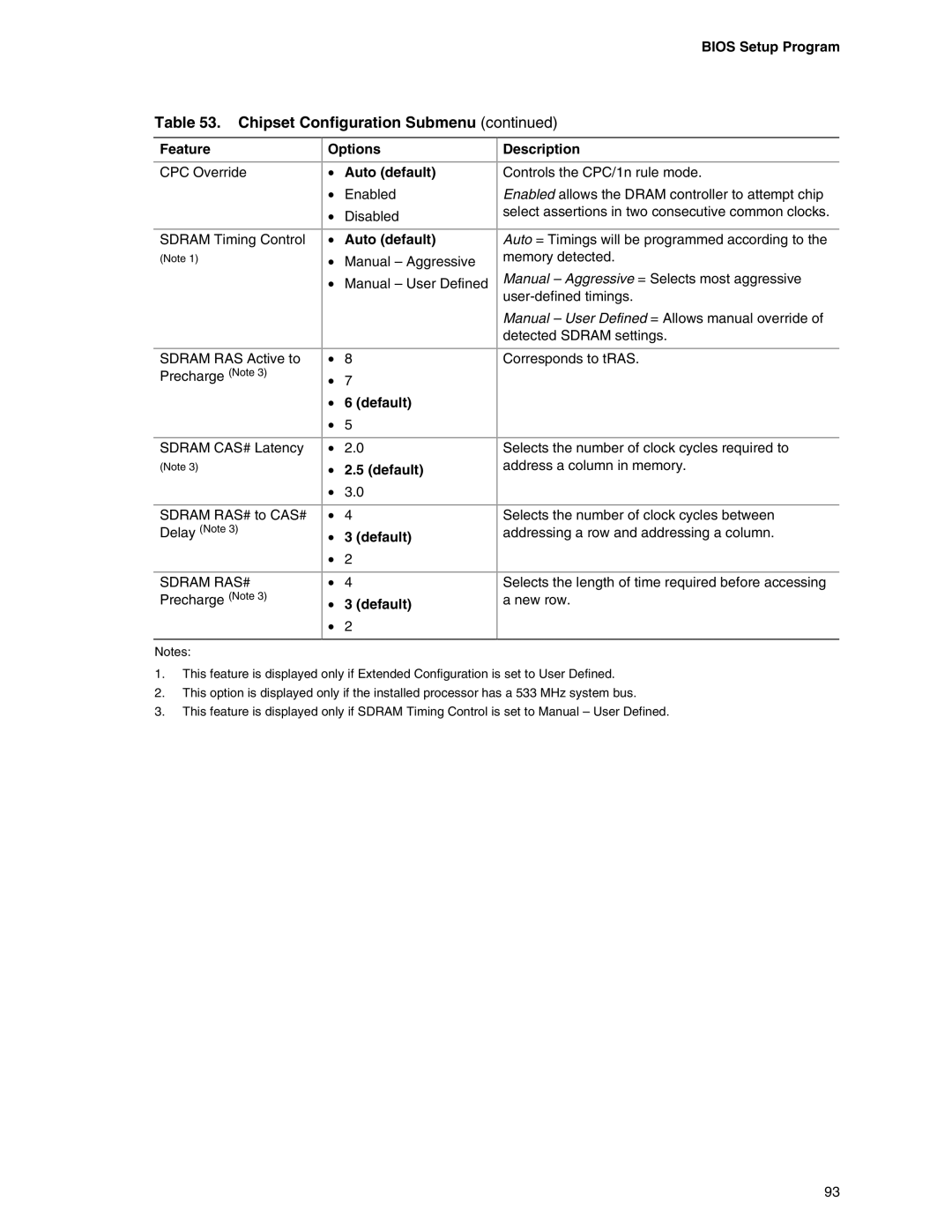

Table 53. Chipset Configuration Submenu (continued)

Feature

CPC Override

SDRAM Timing Control

(Note 1)

SDRAM RAS Active to Precharge (Note 3)

SDRAM CAS# Latency

(Note 3)

SDRAM RAS# to CAS#

Delay (Note 3)

SDRAM RAS#

Precharge (Note 3)

Notes:

Options

•Auto (default)

•Enabled

•Disabled

•Auto (default)

•Manual – Aggressive

•Manual – User Defined

•8

•7

•6 (default)

•5

•2.0

•2.5 (default)

•3.0

•4

•3 (default)

•2

•4

•3 (default)

•2

Description

Controls the CPC/1n rule mode.

Enabled allows the DRAM controller to attempt chip select assertions in two consecutive common clocks.

Auto = Timings will be programmed according to the memory detected.

Manual – Aggressive = Selects most aggressive

Manual – User Defined = Allows manual override of detected SDRAM settings.

Corresponds to tRAS.

Selects the number of clock cycles required to address a column in memory.

Selects the number of clock cycles between addressing a row and addressing a column.

Selects the length of time required before accessing a new row.

1.This feature is displayed only if Extended Configuration is set to User Defined.

2.This option is displayed only if the installed processor has a 533 MHz system bus.

3.This feature is displayed only if SDRAM Timing Control is set to Manual – User Defined.

93