Error Messages and Beep Codes

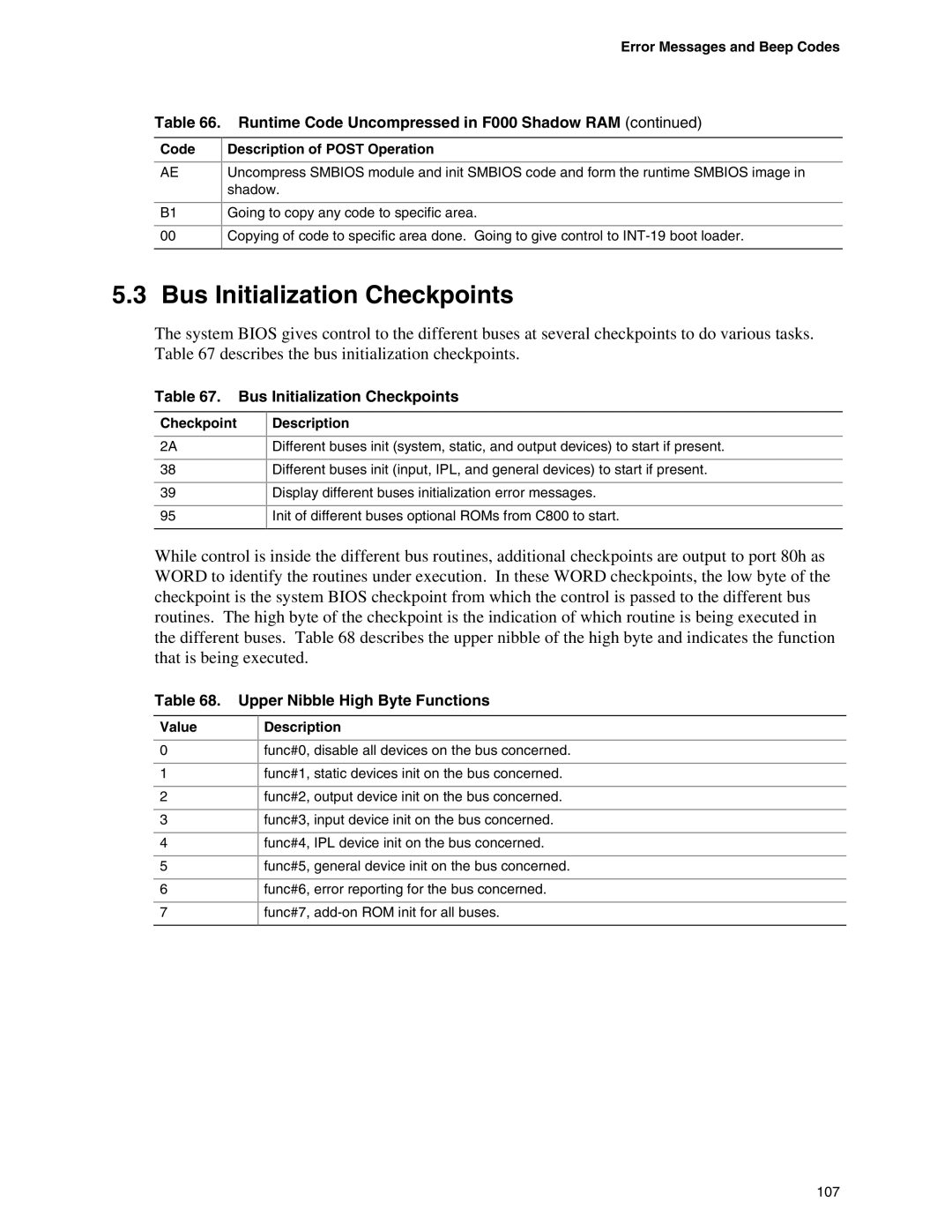

Table 66. Runtime Code Uncompressed in F000 Shadow RAM (continued)

Code

AE

B1

00

Description of POST Operation

Uncompress SMBIOS module and init SMBIOS code and form the runtime SMBIOS image in shadow.

Going to copy any code to specific area.

Copying of code to specific area done. Going to give control to

5.3 Bus Initialization Checkpoints

The system BIOS gives control to the different buses at several checkpoints to do various tasks. Table 67 describes the bus initialization checkpoints.

Table 67. Bus Initialization Checkpoints

Checkpoint

2A

38

39

95

Description

Different buses init (system, static, and output devices) to start if present.

Different buses init (input, IPL, and general devices) to start if present.

Display different buses initialization error messages.

Init of different buses optional ROMs from C800 to start.

While control is inside the different bus routines, additional checkpoints are output to port 80h as WORD to identify the routines under execution. In these WORD checkpoints, the low byte of the checkpoint is the system BIOS checkpoint from which the control is passed to the different bus routines. The high byte of the checkpoint is the indication of which routine is being executed in the different buses. Table 68 describes the upper nibble of the high byte and indicates the function that is being executed.

Table 68. Upper Nibble High Byte Functions

Value

0

1

2

3

4

5

6

7

Description

func#0, disable all devices on the bus concerned.

func#1, static devices init on the bus concerned.

func#2, output device init on the bus concerned.

func#3, input device init on the bus concerned.

func#4, IPL device init on the bus concerned.

func#5, general device init on the bus concerned.

func#6, error reporting for the bus concerned.

func#7,

107