SSI

ERP2U Power Supply Design Guide, V1.0

8.2PWOK (Power OK)

STATUS

Required

PWOK is a power OK signal and will be pulled HIGH by the power supply to indicate that all the outputs are within the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power has been removed for a time sufficiently long so that power supply operation is no longer guaranteed, PWOK will be deasserted to a LOW state. See Figure 3 for a representation of the timing characteristics of PWOK. The start of the PWOK delay time shall be inhibited as long as any power supply output is in current limit.

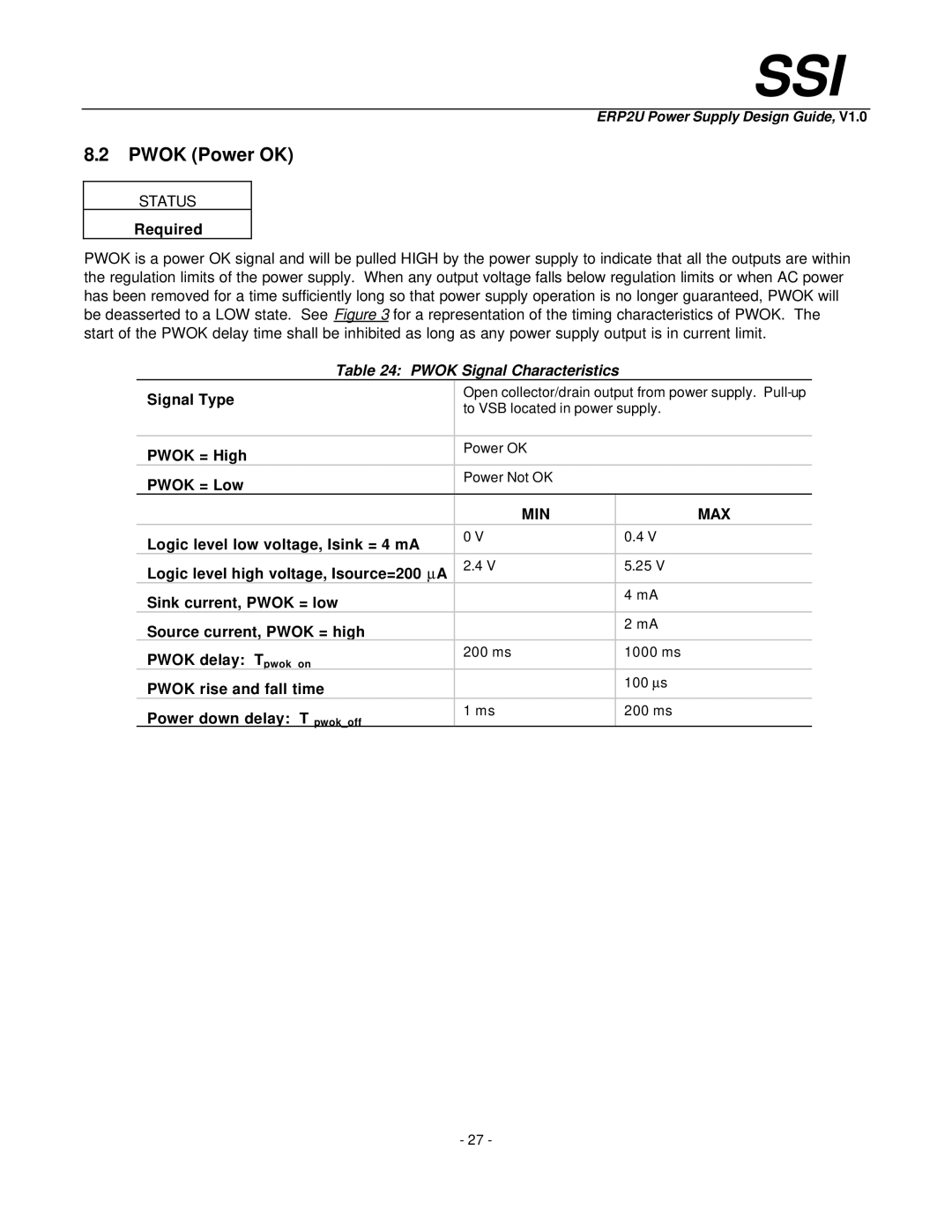

Table 24: PWOK Signal Characteristics

Signal Type | Open collector/drain output from power supply. | |

to VSB located in power supply. | ||

| ||

|

| |

PWOK = High | Power OK | |

| ||

PWOK = Low | Power Not OK | |

|

| MIN | MAX |

Logic level low voltage, Isink = 4 mA | 0 V | 0.4 V |

|

| |

Logic level high voltage, Isource=200 μA | 2.4 V | 5.25 V |

|

| |

Sink current, PWOK = low |

| 4 mA |

|

| |

Source current, PWOK = high |

| 2 mA |

|

| |

PWOK delay: Tpwok_on | 200 ms | 1000 ms |

|

| |

PWOK rise and fall time |

| 100 μs |

|

| |

Power down delay: T pwok_off | 1 ms | 200 ms |

|

|

- 27 -