|

|

|

|

| English |

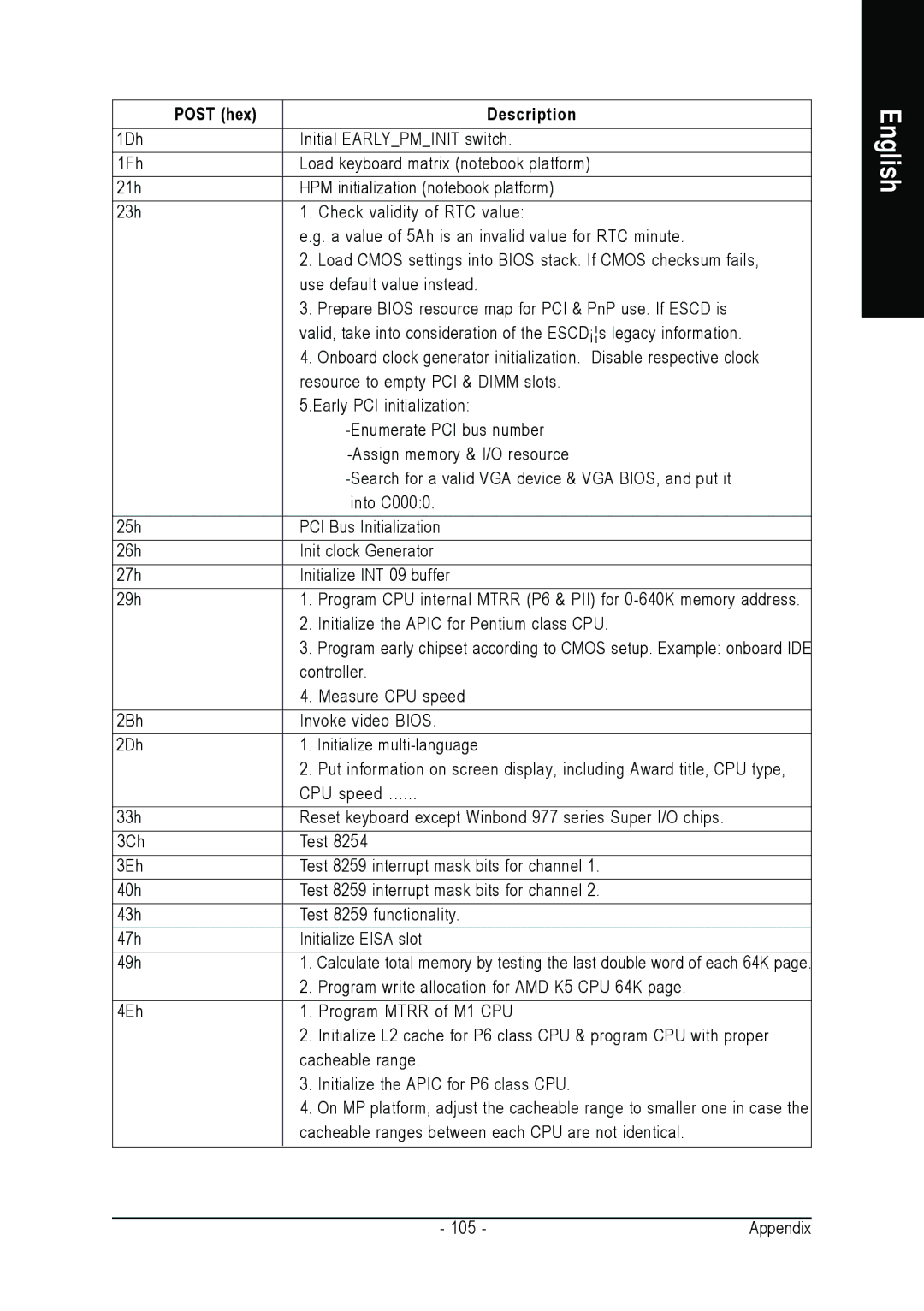

POST (hex) |

| Description |

|

| |

|

|

|

| ||

1Dh | Initial EARLY_PM_INIT switch. |

|

| ||

1Fh | Load keyboard matrix (notebook platform) |

|

| ||

21h | HPM initialization (notebook platform) |

|

| ||

23h | 1. | Check validity of RTC value: |

|

|

|

| e.g. a value of 5Ah is an invalid value for RTC minute. |

|

| ||

| 2. | Load CMOS settings into BIOS stack. If CMOS checksum fails, |

|

| |

| use default value instead. |

|

|

| |

| 3. | Prepare BIOS resource map for PCI & PnP use. If ESCD is |

|

| |

| valid, take into consideration of the ESCD¡¦s legacy information. |

| |||

| 4. | Onboard clock generator initialization. | Disable respective clock |

| |

| resource to empty PCI & DIMM slots. |

|

|

| |

| 5.Early PCI initialization: |

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

| |||

|

| into C000:0. |

|

|

|

25h | PCI Bus Initialization |

|

|

| |

26h | Init clock Generator |

|

|

| |

27h | Initialize INT 09 buffer |

|

|

| |

29h | 1. | Program CPU internal MTRR (P6 & PII) for |

| ||

| 2. | Initialize the APIC for Pentium class CPU. |

| ||

| 3. Program early chipset according to CMOS setup. Example: onboard IDE |

| |||

| controller. |

|

|

| |

| 4. Measure CPU speed |

|

|

| |

2Bh | Invoke video BIOS. |

|

|

| |

2Dh | 1. | Initialize |

|

|

|

| 2. | Put information on screen display, including Award title, CPU type, |

| ||

| CPU speed |

|

|

| |

33h | Reset keyboard except Winbond 977 series Super I/O chips. |

| |||

3Ch | Test 8254 |

|

|

| |

3Eh | Test 8259 interrupt mask bits for channel 1. |

| |||

40h | Test 8259 interrupt mask bits for channel 2. |

| |||

43h | Test 8259 functionality. |

|

|

| |

47h | Initialize EISA slot |

|

|

| |

49h | 1. Calculate total memory by testing the last double word of each 64K page. |

| |||

| 2. | Program write allocation for AMD K5 CPU 64K page. |

| ||

4Eh | 1. Program MTRR of M1 CPU |

|

|

| |

| 2. | Initialize L2 cache for P6 class CPU & program CPU with proper |

| ||

| cacheable range. |

|

|

| |

| 3. | Initialize the APIC for P6 class CPU. |

|

|

|

| 4. | On MP platform, adjust the cacheable range to smaller one in case the |

| ||

| cacheable ranges between each CPU are not identical. |

| |||

- 105 - | Appendix |