5.2.2.1 Scan List Queue Programming

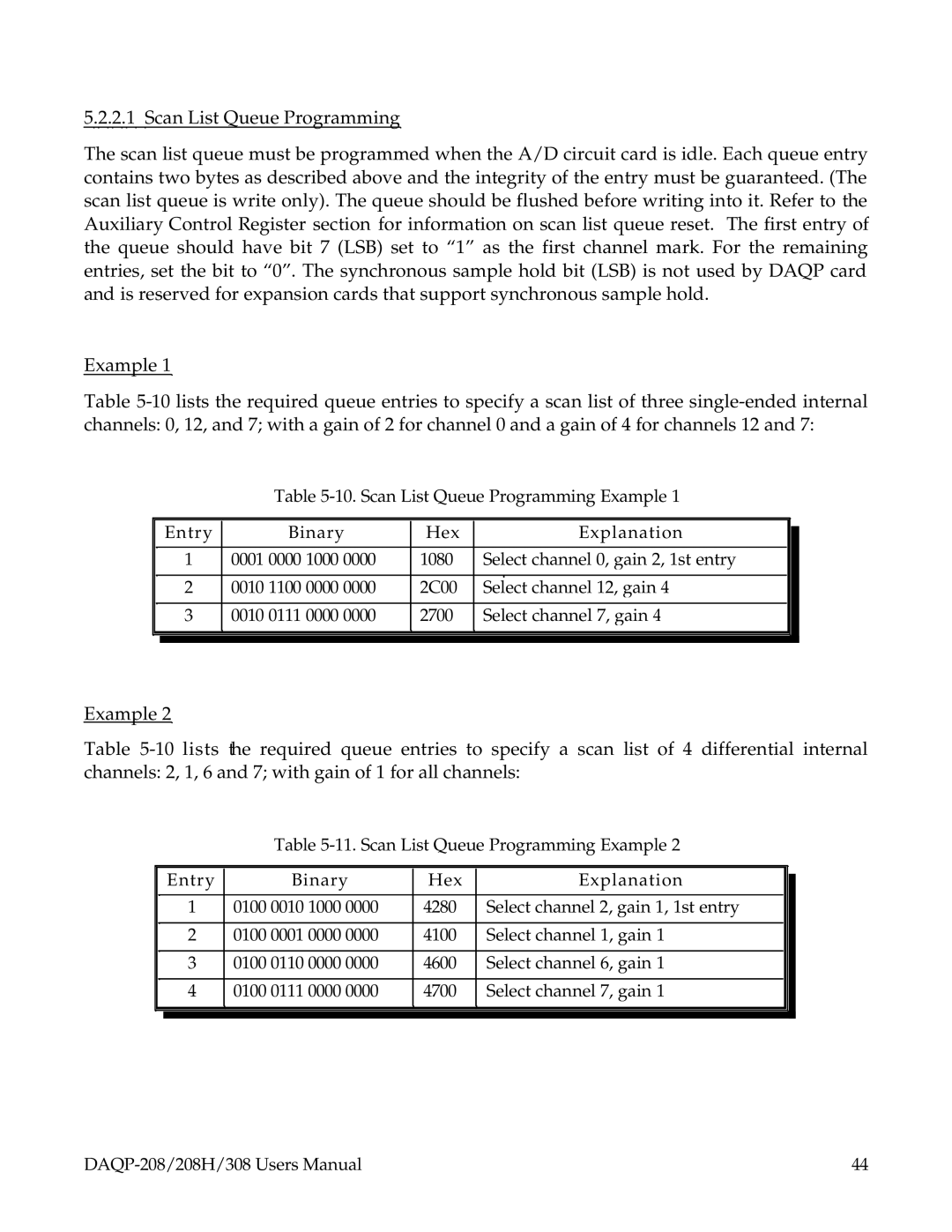

The scan list queue must be programmed when the A/D circuit card is idle. Each queue entry contains two bytes as described above and the integrity of the entry must be guaranteed. (The scan list queue is write only). The queue should be flushed before writing into it. Refer to the Auxiliary Control Register section for information on scan list queue reset. The first entry of the queue should have bit 7 (LSB) set to “1” as the first channel mark. For the remaining entries, set the bit to “0”. The synchronous sample hold bit (LSB) is not used by DAQP card and is reserved for expansion cards that support synchronous sample hold.

Example 1

Table

Table

| Entry | Binary | Hex | Explanation |

| |

|

| |||||

|

|

|

|

|

| |

| 1 | 0001 0000 1000 0000 | 1080 | Select channel 0, gain 2, 1st entry |

|

|

| 2 | 0010 1100 0000 0000 | 2C00 | entry |

|

|

| Select channel 12, gain 4 |

| ||||

| 3 | 0010 0111 0000 0000 | 2700 | Select channel 7, gain 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Example 2

Table

Table

| Entry | Binary | Hex | Explanation |

| |

|

| |||||

|

|

|

|

|

| |

| 1 | 0100 0010 1000 0000 | 4280 | Select channel 2, gain 1, 1st entry |

|

|

|

|

|

|

|

| |

| 2 | 0100 0001 0000 0000 | 4100 | Select channel 1, gain 1 |

|

|

|

|

|

|

|

| |

| 3 | 0100 0110 0000 0000 | 4600 | Select channel 6, gain 1 |

|

|

|

|

|

|

|

| |

| 4 | 0100 0111 0000 0000 | 4700 | Select channel 7, gain 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |