33

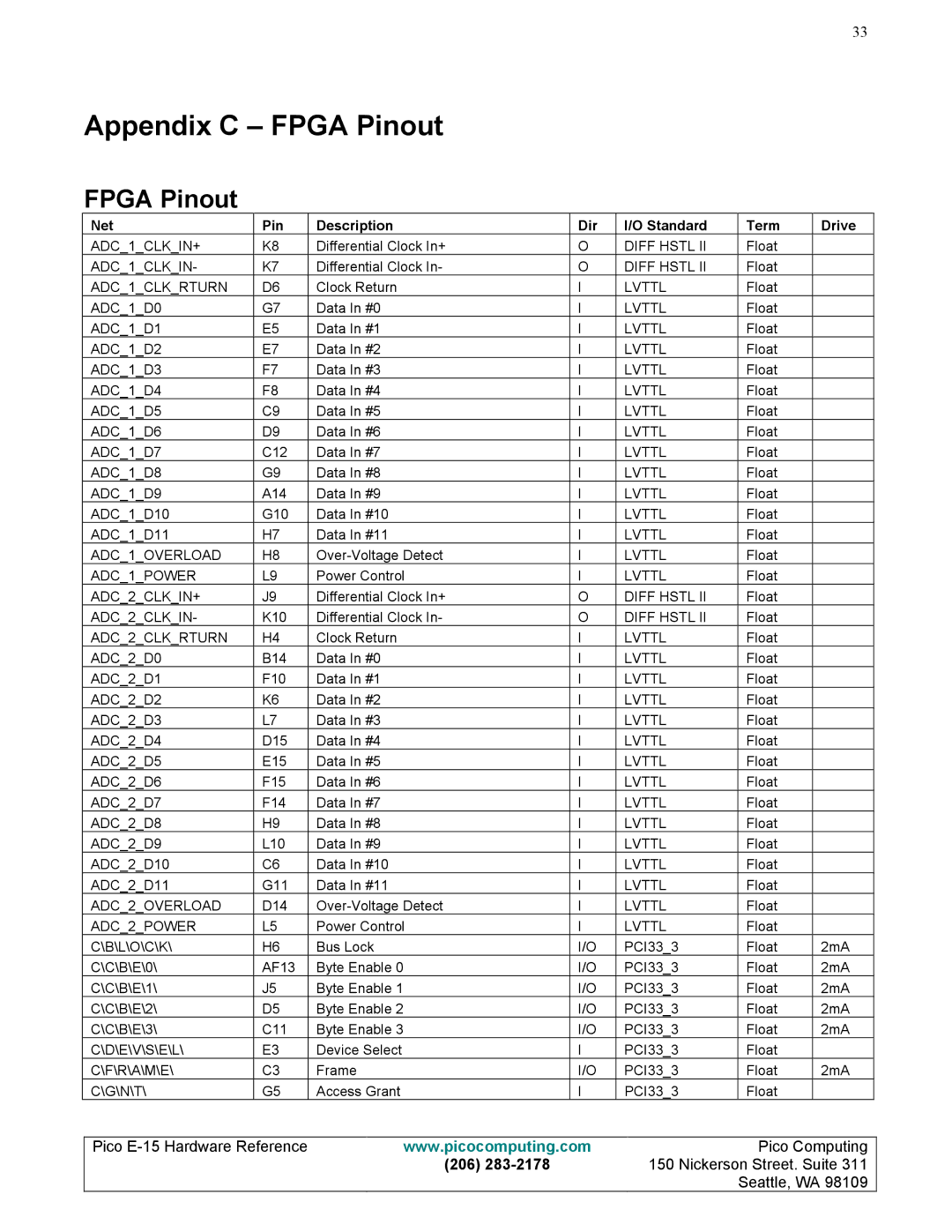

Appendix C – FPGA Pinout

FPGA Pinout

Net | Pin | Description | Dir | I/O Standard | Term | Drive |

ADC_1_CLK_IN+ | K8 | Differential Clock In+ | O | DIFF HSTL II | Float |

|

ADC_1_CLK_IN- | K7 | Differential Clock In- | O | DIFF HSTL II | Float |

|

ADC_1_CLK_RTURN | D6 | Clock Return | I | LVTTL | Float |

|

ADC_1_D0 | G7 | Data In #0 | I | LVTTL | Float |

|

ADC_1_D1 | E5 | Data In #1 | I | LVTTL | Float |

|

ADC_1_D2 | E7 | Data In #2 | I | LVTTL | Float |

|

ADC_1_D3 | F7 | Data In #3 | I | LVTTL | Float |

|

ADC_1_D4 | F8 | Data In #4 | I | LVTTL | Float |

|

ADC_1_D5 | C9 | Data In #5 | I | LVTTL | Float |

|

ADC_1_D6 | D9 | Data In #6 | I | LVTTL | Float |

|

ADC_1_D7 | C12 | Data In #7 | I | LVTTL | Float |

|

ADC_1_D8 | G9 | Data In #8 | I | LVTTL | Float |

|

ADC_1_D9 | A14 | Data In #9 | I | LVTTL | Float |

|

ADC_1_D10 | G10 | Data In #10 | I | LVTTL | Float |

|

ADC_1_D11 | H7 | Data In #11 | I | LVTTL | Float |

|

ADC_1_OVERLOAD | H8 | I | LVTTL | Float |

| |

ADC_1_POWER | L9 | Power Control | I | LVTTL | Float |

|

ADC_2_CLK_IN+ | J9 | Differential Clock In+ | O | DIFF HSTL II | Float |

|

ADC_2_CLK_IN- | K10 | Differential Clock In- | O | DIFF HSTL II | Float |

|

ADC_2_CLK_RTURN | H4 | Clock Return | I | LVTTL | Float |

|

ADC_2_D0 | B14 | Data In #0 | I | LVTTL | Float |

|

ADC_2_D1 | F10 | Data In #1 | I | LVTTL | Float |

|

ADC_2_D2 | K6 | Data In #2 | I | LVTTL | Float |

|

ADC_2_D3 | L7 | Data In #3 | I | LVTTL | Float |

|

ADC_2_D4 | D15 | Data In #4 | I | LVTTL | Float |

|

ADC_2_D5 | E15 | Data In #5 | I | LVTTL | Float |

|

ADC_2_D6 | F15 | Data In #6 | I | LVTTL | Float |

|

ADC_2_D7 | F14 | Data In #7 | I | LVTTL | Float |

|

ADC_2_D8 | H9 | Data In #8 | I | LVTTL | Float |

|

ADC_2_D9 | L10 | Data In #9 | I | LVTTL | Float |

|

ADC_2_D10 | C6 | Data In #10 | I | LVTTL | Float |

|

ADC_2_D11 | G11 | Data In #11 | I | LVTTL | Float |

|

ADC_2_OVERLOAD | D14 | I | LVTTL | Float |

| |

ADC_2_POWER | L5 | Power Control | I | LVTTL | Float |

|

C\B\L\O\C\K\ | H6 | Bus Lock | I/O | PCI33_3 | Float | 2mA |

C\C\B\E\0\ | AF13 | Byte Enable 0 | I/O | PCI33_3 | Float | 2mA |

C\C\B\E\1\ | J5 | Byte Enable 1 | I/O | PCI33_3 | Float | 2mA |

C\C\B\E\2\ | D5 | Byte Enable 2 | I/O | PCI33_3 | Float | 2mA |

C\C\B\E\3\ | C11 | Byte Enable 3 | I/O | PCI33_3 | Float | 2mA |

C\D\E\V\S\E\L\ | E3 | Device Select | I | PCI33_3 | Float |

|

C\F\R\A\M\E\ | C3 | Frame | I/O | PCI33_3 | Float | 2mA |

C\G\N\T\ | G5 | Access Grant | I | PCI33_3 | Float |

|

Pico | www.picocomputing.com | Pico Computing |

| (206) | 150 Nickerson Street. Suite 311 |

|

| Seattle, WA 98109 |