40

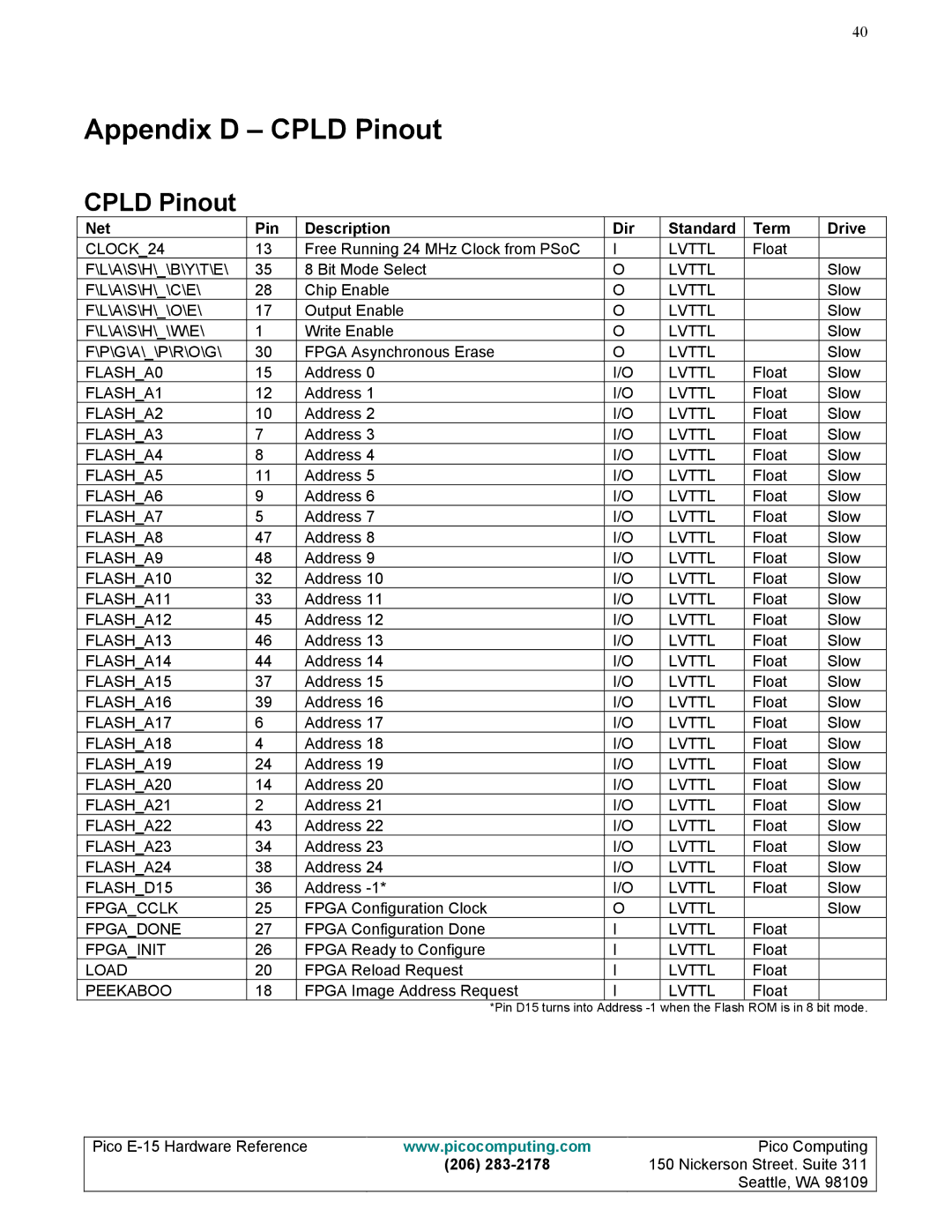

Appendix D – CPLD Pinout

CPLD Pinout

Net | Pin | Description | Dir | Standard | Term | Drive |

CLOCK_24 | 13 | Free Running 24 MHz Clock from PSoC | I | LVTTL | Float |

|

F\L\A\S\H\_\B\Y\T\E\ | 35 | 8 Bit Mode Select | O | LVTTL |

| Slow |

F\L\A\S\H\_\C\E\ | 28 | Chip Enable | O | LVTTL |

| Slow |

F\L\A\S\H\_\O\E\ | 17 | Output Enable | O | LVTTL |

| Slow |

F\L\A\S\H\_\W\E\ | 1 | Write Enable | O | LVTTL |

| Slow |

F\P\G\A\_\P\R\O\G\ | 30 | FPGA Asynchronous Erase | O | LVTTL |

| Slow |

FLASH_A0 | 15 | Address 0 | I/O | LVTTL | Float | Slow |

FLASH_A1 | 12 | Address 1 | I/O | LVTTL | Float | Slow |

FLASH_A2 | 10 | Address 2 | I/O | LVTTL | Float | Slow |

FLASH_A3 | 7 | Address 3 | I/O | LVTTL | Float | Slow |

FLASH_A4 | 8 | Address 4 | I/O | LVTTL | Float | Slow |

FLASH_A5 | 11 | Address 5 | I/O | LVTTL | Float | Slow |

FLASH_A6 | 9 | Address 6 | I/O | LVTTL | Float | Slow |

FLASH_A7 | 5 | Address 7 | I/O | LVTTL | Float | Slow |

FLASH_A8 | 47 | Address 8 | I/O | LVTTL | Float | Slow |

FLASH_A9 | 48 | Address 9 | I/O | LVTTL | Float | Slow |

FLASH_A10 | 32 | Address 10 | I/O | LVTTL | Float | Slow |

FLASH_A11 | 33 | Address 11 | I/O | LVTTL | Float | Slow |

FLASH_A12 | 45 | Address 12 | I/O | LVTTL | Float | Slow |

FLASH_A13 | 46 | Address 13 | I/O | LVTTL | Float | Slow |

FLASH_A14 | 44 | Address 14 | I/O | LVTTL | Float | Slow |

FLASH_A15 | 37 | Address 15 | I/O | LVTTL | Float | Slow |

FLASH_A16 | 39 | Address 16 | I/O | LVTTL | Float | Slow |

FLASH_A17 | 6 | Address 17 | I/O | LVTTL | Float | Slow |

FLASH_A18 | 4 | Address 18 | I/O | LVTTL | Float | Slow |

FLASH_A19 | 24 | Address 19 | I/O | LVTTL | Float | Slow |

FLASH_A20 | 14 | Address 20 | I/O | LVTTL | Float | Slow |

FLASH_A21 | 2 | Address 21 | I/O | LVTTL | Float | Slow |

FLASH_A22 | 43 | Address 22 | I/O | LVTTL | Float | Slow |

FLASH_A23 | 34 | Address 23 | I/O | LVTTL | Float | Slow |

FLASH_A24 | 38 | Address 24 | I/O | LVTTL | Float | Slow |

FLASH_D15 | 36 | Address | I/O | LVTTL | Float | Slow |

FPGA_CCLK | 25 | FPGA Configuration Clock | O | LVTTL |

| Slow |

FPGA_DONE | 27 | FPGA Configuration Done | I | LVTTL | Float |

|

FPGA_INIT | 26 | FPGA Ready to Configure | I | LVTTL | Float |

|

LOAD | 20 | FPGA Reload Request | I | LVTTL | Float |

|

PEEKABOO | 18 | FPGA Image Address Request | I | LVTTL | Float |

|

|

| *Pin D15 turns into Address | ||||

Pico | www.picocomputing.com | Pico Computing |

| (206) | 150 Nickerson Street. Suite 311 |

|

| Seattle, WA 98109 |