35

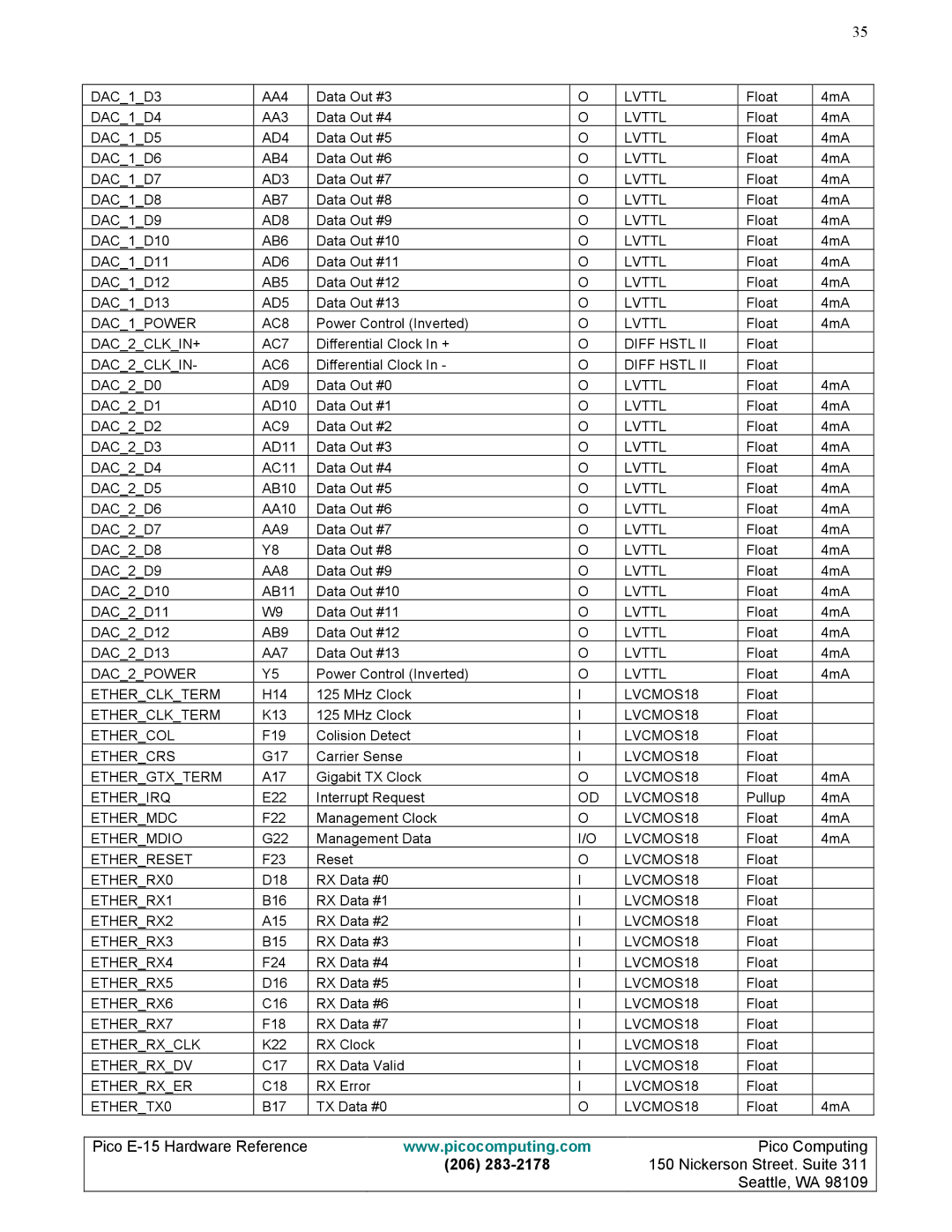

DAC_1_D3 | AA4 | Data Out #3 | O | LVTTL | Float | 4mA |

DAC_1_D4 | AA3 | Data Out #4 | O | LVTTL | Float | 4mA |

DAC_1_D5 | AD4 | Data Out #5 | O | LVTTL | Float | 4mA |

DAC_1_D6 | AB4 | Data Out #6 | O | LVTTL | Float | 4mA |

DAC_1_D7 | AD3 | Data Out #7 | O | LVTTL | Float | 4mA |

DAC_1_D8 | AB7 | Data Out #8 | O | LVTTL | Float | 4mA |

DAC_1_D9 | AD8 | Data Out #9 | O | LVTTL | Float | 4mA |

DAC_1_D10 | AB6 | Data Out #10 | O | LVTTL | Float | 4mA |

DAC_1_D11 | AD6 | Data Out #11 | O | LVTTL | Float | 4mA |

DAC_1_D12 | AB5 | Data Out #12 | O | LVTTL | Float | 4mA |

DAC_1_D13 | AD5 | Data Out #13 | O | LVTTL | Float | 4mA |

DAC_1_POWER | AC8 | Power Control (Inverted) | O | LVTTL | Float | 4mA |

DAC_2_CLK_IN+ | AC7 | Differential Clock In + | O | DIFF HSTL II | Float |

|

DAC_2_CLK_IN- | AC6 | Differential Clock In - | O | DIFF HSTL II | Float |

|

DAC_2_D0 | AD9 | Data Out #0 | O | LVTTL | Float | 4mA |

DAC_2_D1 | AD10 | Data Out #1 | O | LVTTL | Float | 4mA |

DAC_2_D2 | AC9 | Data Out #2 | O | LVTTL | Float | 4mA |

DAC_2_D3 | AD11 | Data Out #3 | O | LVTTL | Float | 4mA |

DAC_2_D4 | AC11 | Data Out #4 | O | LVTTL | Float | 4mA |

DAC_2_D5 | AB10 | Data Out #5 | O | LVTTL | Float | 4mA |

DAC_2_D6 | AA10 | Data Out #6 | O | LVTTL | Float | 4mA |

DAC_2_D7 | AA9 | Data Out #7 | O | LVTTL | Float | 4mA |

DAC_2_D8 | Y8 | Data Out #8 | O | LVTTL | Float | 4mA |

DAC_2_D9 | AA8 | Data Out #9 | O | LVTTL | Float | 4mA |

DAC_2_D10 | AB11 | Data Out #10 | O | LVTTL | Float | 4mA |

DAC_2_D11 | W9 | Data Out #11 | O | LVTTL | Float | 4mA |

DAC_2_D12 | AB9 | Data Out #12 | O | LVTTL | Float | 4mA |

DAC_2_D13 | AA7 | Data Out #13 | O | LVTTL | Float | 4mA |

DAC_2_POWER | Y5 | Power Control (Inverted) | O | LVTTL | Float | 4mA |

ETHER_CLK_TERM | H14 | 125 MHz Clock | I | LVCMOS18 | Float |

|

ETHER_CLK_TERM | K13 | 125 MHz Clock | I | LVCMOS18 | Float |

|

ETHER_COL | F19 | Colision Detect | I | LVCMOS18 | Float |

|

ETHER_CRS | G17 | Carrier Sense | I | LVCMOS18 | Float |

|

ETHER_GTX_TERM | A17 | Gigabit TX Clock | O | LVCMOS18 | Float | 4mA |

ETHER_IRQ | E22 | Interrupt Request | OD | LVCMOS18 | Pullup | 4mA |

ETHER_MDC | F22 | Management Clock | O | LVCMOS18 | Float | 4mA |

ETHER_MDIO | G22 | Management Data | I/O | LVCMOS18 | Float | 4mA |

ETHER_RESET | F23 | Reset | O | LVCMOS18 | Float |

|

ETHER_RX0 | D18 | RX Data #0 | I | LVCMOS18 | Float |

|

ETHER_RX1 | B16 | RX Data #1 | I | LVCMOS18 | Float |

|

ETHER_RX2 | A15 | RX Data #2 | I | LVCMOS18 | Float |

|

ETHER_RX3 | B15 | RX Data #3 | I | LVCMOS18 | Float |

|

ETHER_RX4 | F24 | RX Data #4 | I | LVCMOS18 | Float |

|

ETHER_RX5 | D16 | RX Data #5 | I | LVCMOS18 | Float |

|

ETHER_RX6 | C16 | RX Data #6 | I | LVCMOS18 | Float |

|

ETHER_RX7 | F18 | RX Data #7 | I | LVCMOS18 | Float |

|

ETHER_RX_CLK | K22 | RX Clock | I | LVCMOS18 | Float |

|

ETHER_RX_DV | C17 | RX Data Valid | I | LVCMOS18 | Float |

|

ETHER_RX_ER | C18 | RX Error | I | LVCMOS18 | Float |

|

ETHER_TX0 | B17 | TX Data #0 | O | LVCMOS18 | Float | 4mA |

Pico | www.picocomputing.com | Pico Computing |

| (206) | 150 Nickerson Street. Suite 311 |

|

| Seattle, WA 98109 |