|

|

|

|

|

| 38 |

|

|

|

|

|

|

|

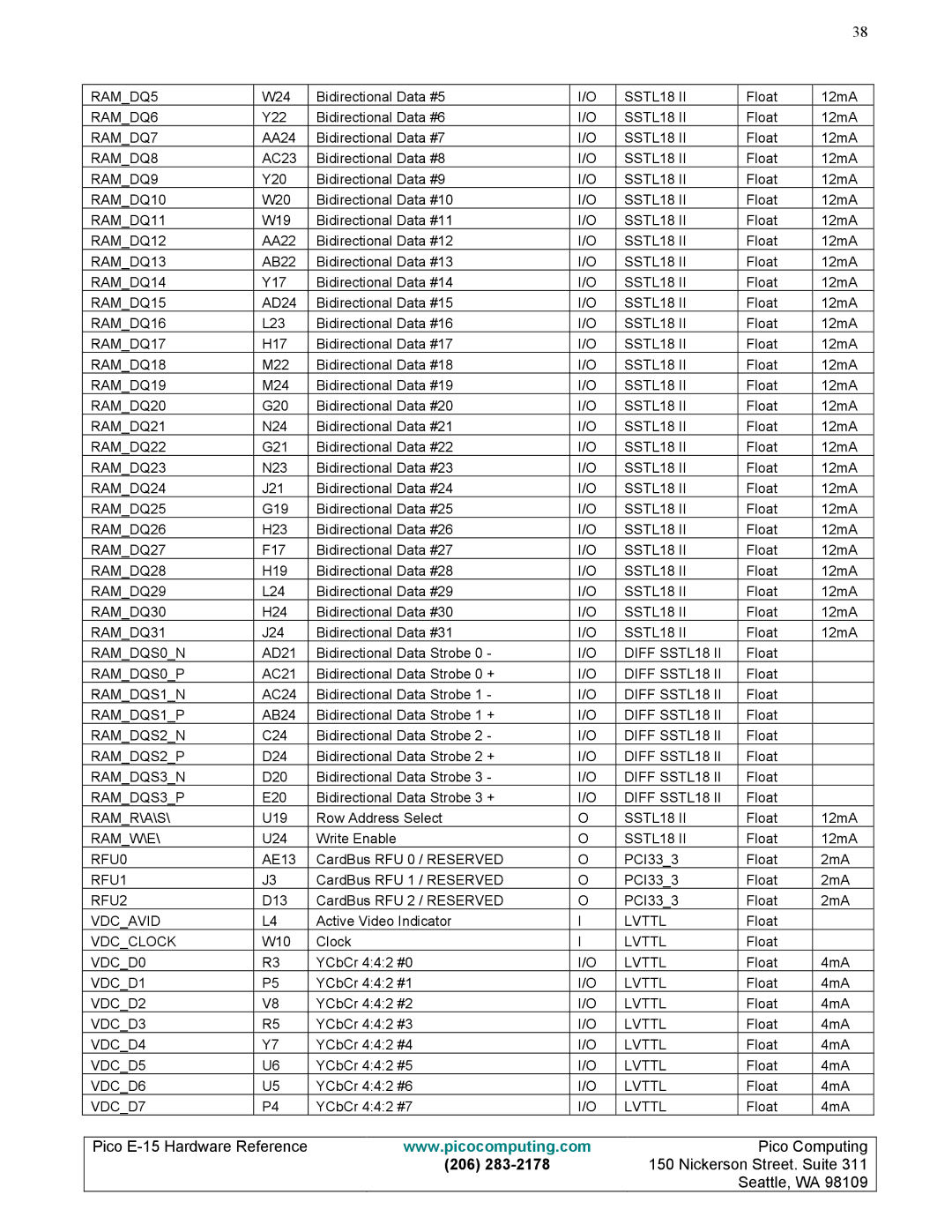

RAM_DQ5 | W24 | Bidirectional Data #5 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ6 | Y22 | Bidirectional Data #6 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ7 | AA24 | Bidirectional Data #7 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ8 | AC23 | Bidirectional Data #8 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ9 | Y20 | Bidirectional Data #9 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ10 | W20 | Bidirectional Data #10 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ11 | W19 | Bidirectional Data #11 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ12 | AA22 | Bidirectional Data #12 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ13 | AB22 | Bidirectional Data #13 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ14 | Y17 | Bidirectional Data #14 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ15 | AD24 | Bidirectional Data #15 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ16 | L23 | Bidirectional Data #16 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ17 | H17 | Bidirectional Data #17 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ18 | M22 | Bidirectional Data #18 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ19 | M24 | Bidirectional Data #19 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ20 | G20 | Bidirectional Data #20 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ21 | N24 | Bidirectional Data #21 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ22 | G21 | Bidirectional Data #22 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ23 | N23 | Bidirectional Data #23 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ24 | J21 | Bidirectional Data #24 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ25 | G19 | Bidirectional Data #25 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ26 | H23 | Bidirectional Data #26 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ27 | F17 | Bidirectional Data #27 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ28 | H19 | Bidirectional Data #28 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ29 | L24 | Bidirectional Data #29 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ30 | H24 | Bidirectional Data #30 | I/O | SSTL18 II | Float | 12mA |

RAM_DQ31 | J24 | Bidirectional Data #31 | I/O | SSTL18 II | Float | 12mA |

RAM_DQS0_N | AD21 | Bidirectional Data Strobe 0 - | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS0_P | AC21 | Bidirectional Data Strobe 0 + | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS1_N | AC24 | Bidirectional Data Strobe 1 - | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS1_P | AB24 | Bidirectional Data Strobe 1 + | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS2_N | C24 | Bidirectional Data Strobe 2 - | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS2_P | D24 | Bidirectional Data Strobe 2 + | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS3_N | D20 | Bidirectional Data Strobe 3 - | I/O | DIFF SSTL18 II | Float |

|

RAM_DQS3_P | E20 | Bidirectional Data Strobe 3 + | I/O | DIFF SSTL18 II | Float |

|

RAM_R\A\S\ | U19 | Row Address Select | O | SSTL18 II | Float | 12mA |

RAM_W\E\ | U24 | Write Enable | O | SSTL18 II | Float | 12mA |

RFU0 | AE13 | CardBus RFU 0 / RESERVED | O | PCI33_3 | Float | 2mA |

RFU1 | J3 | CardBus RFU 1 / RESERVED | O | PCI33_3 | Float | 2mA |

RFU2 | D13 | CardBus RFU 2 / RESERVED | O | PCI33_3 | Float | 2mA |

VDC_AVID | L4 | Active Video Indicator | I | LVTTL | Float |

|

VDC_CLOCK | W10 | Clock | I | LVTTL | Float |

|

VDC_D0 | R3 | YCbCr 4:4:2 #0 | I/O | LVTTL | Float | 4mA |

VDC_D1 | P5 | YCbCr 4:4:2 #1 | I/O | LVTTL | Float | 4mA |

VDC_D2 | V8 | YCbCr 4:4:2 #2 | I/O | LVTTL | Float | 4mA |

VDC_D3 | R5 | YCbCr 4:4:2 #3 | I/O | LVTTL | Float | 4mA |

VDC_D4 | Y7 | YCbCr 4:4:2 #4 | I/O | LVTTL | Float | 4mA |

VDC_D5 | U6 | YCbCr 4:4:2 #5 | I/O | LVTTL | Float | 4mA |

VDC_D6 | U5 | YCbCr 4:4:2 #6 | I/O | LVTTL | Float | 4mA |

VDC_D7 | P4 | YCbCr 4:4:2 #7 | I/O | LVTTL | Float | 4mA |

Pico | www.picocomputing.com | Pico Computing |

| (206) | 150 Nickerson Street. Suite 311 |

|

| Seattle, WA 98109 |